基于FPGA的BCH编解码算法的实现

时间:10-02

整理:3721RD

点击:

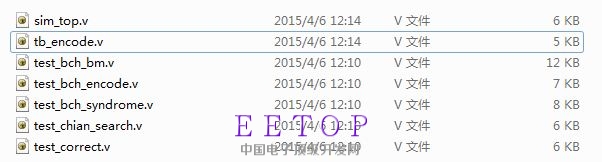

这是之前在网上找的代码的一部分,有哪位大神懂的或原作者,能否交流一下,万分感谢

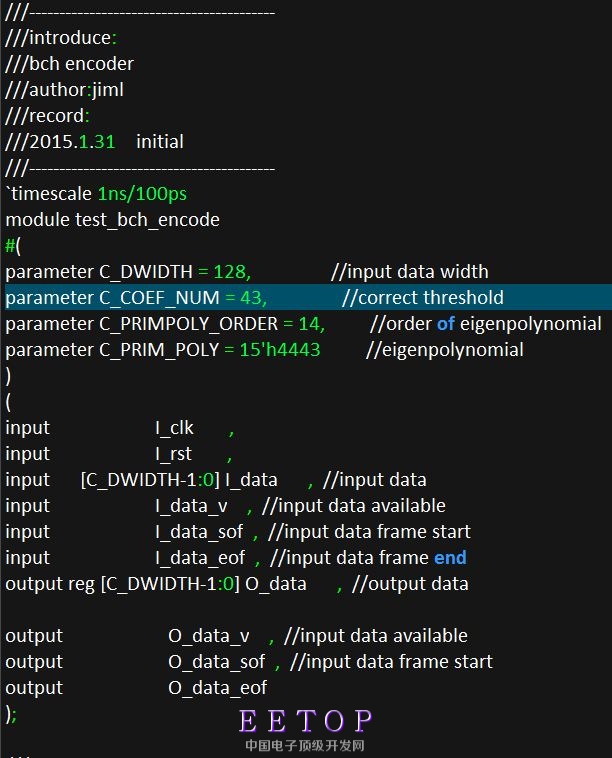

///introduce:

///bch encoder

///author:jiml

///record:

///2015.1.31 initial

///-----------------------------------------

`timescale 1ns/100ps

module test_bch_encode

#(

parameter C_DWIDTH = 128, //input data width

parameter C_COEF_NUM = 43, //correct threshold

parameter C_PRIMPOLY_ORDER = 14, //order of eigenpolynomial

parameter C_PRIM_POLY = 15'h4443 //eigenpolynomial

)

(

input I_clk ,

input I_rst ,

input [C_DWIDTH-1:0] I_data , //input data

input I_data_v , //input data available

input I_data_sof , //input data frame start

input I_data_eof , //input data frame end

output reg [C_DWIDTH-1:0] O_data , //output data

output O_data_v , //input data available

output O_data_sof , //input data frame start

output O_data_eof

);

///----------------------------------------

///parameter and variable

///----------------------------------------

localparam C_REG_LEN = C_COEF_NUM*C_PRIMPOLY_ORDER;

///introduce:

///bch encoder

///author:jiml

///record:

///2015.1.31 initial

///-----------------------------------------

`timescale 1ns/100ps

module test_bch_encode

#(

parameter C_DWIDTH = 128, //input data width

parameter C_COEF_NUM = 43, //correct threshold

parameter C_PRIMPOLY_ORDER = 14, //order of eigenpolynomial

parameter C_PRIM_POLY = 15'h4443 //eigenpolynomial

)

(

input I_clk ,

input I_rst ,

input [C_DWIDTH-1:0] I_data , //input data

input I_data_v , //input data available

input I_data_sof , //input data frame start

input I_data_eof , //input data frame end

output reg [C_DWIDTH-1:0] O_data , //output data

output O_data_v , //input data available

output O_data_sof , //input data frame start

output O_data_eof

);

///----------------------------------------

///parameter and variable

///----------------------------------------

localparam C_REG_LEN = C_COEF_NUM*C_PRIMPOLY_ORDER;

这是testbench?

不是testbench,这是源程序,