再问xilinx ip 核之srio之例化使用

时间:10-02

整理:3721RD

点击:

以前问的太笼统,ip核的example design又很复杂。因此我决定只使用一个简单的功能来入手。这就是HELLO format格式的NWRITE操作。即对简单的写操作进行仿真。但是很可惜,还是有些地方不明白,而且仿不出结果来,因此再来问一问,希望能得到您的解答(万分期待):

这是一个模块

module srio_nwrite_gen(

input log_clk,

input log_rst,

input val_ireq_tready,

// input [15:0] src_id,

// input [15:0] dest_id,

// input [15:0] source_id,

output reg val_ireq_tvalid,

// input val_ireq_tready,

// output reg val_ireq_tlast,

output reg [63:0] val_ireq_tdata,

output [7:0] val_ireq_tkeep,

output [31:0] val_ireq_tuser

);

localparam [7:0] src_id=8'hff;

localparam [7:0] dest_id=8'hff;

localparam [3:0] NWRITE=4'd5;

localparam [3:0] TNWR =4'd4;

localparam [64*19-1:0] nwrite_instruction = {

// NWRITEs

{12'h000, NWRITE, TNWR, 36'h198877600, 8'd5},

{12'h000, NWRITE, TNWR, 36'h198877601, 8'd6},

{12'h000, NWRITE, TNWR, 36'h2ABBCCDD8, 8'd6},

{12'h000, NWRITE, TNWR, 36'h2ABBCCDD8, 8'd7},

{12'h000, NWRITE, TNWR, 36'h2ABBCCDD8, 8'd15},

{12'h000, NWRITE, TNWR, 36'h2ABBCCDD8, 8'd31},

{12'h000, NWRITE, TNWR, 36'h120000600, 8'd63},

{12'h000, NWRITE, TNWR, 36'h230000600, 8'd95},

{12'h000, NWRITE, TNWR, 36'h340000600, 8'd127},

{12'h000, NWRITE, TNWR, 36'h450000600, 8'd255},

{12'h000, NWRITE, TNWR, 36'h560000600, 8'd15},

{12'h000, NWRITE, TNWR, 36'h670000600, 8'd31},

{12'h000, NWRITE, TNWR, 36'h780000600, 8'd63},

{12'h000, NWRITE, TNWR, 36'h890000600, 8'd95},

{12'h000, NWRITE, TNWR, 36'h9A0000600, 8'd127},

{12'h000, NWRITE, TNWR, 36'hAB0000600, 8'd255},

{12'h000, NWRITE, TNWR, 36'hBC0000600, 8'd15},

{12'h000, NWRITE, TNWR, 36'hCD0000600, 8'd15},

{12'h000, NWRITE, TNWR, 36'hDE0000600, 8'd15}};

wire [63:0] instruction[0:18];

genvar ii;

generate

for (ii = 0; ii <19; ii = ii + 1) begin : instruction_gen

assign instruction[ii] = nwrite_instruction[(ii+1)*64-1:ii*64];

end

endgenerate

reg [4:0] i;

reg val_ireq_tlast;

always @(posedge log_clk or negedge log_rst)

if(log_rst)

begin

val_ireq_tvalid<=1'b0;

val_ireq_tdata<=64'd0;

val_ireq_tlast<=1'b0;

i<=4'd0;

end

else

begin

if(val_ireq_tready)

begin

case(i)

0,1,2,3,4,5,6,7,8,9,10,11,12,13,14,15,16,17:

begin

val_ireq_tvalid<=1'b1;

val_ireq_tdata<=instruction;

val_ireq_tlast<=1'b0;

i<=i+1'b1;

end

18:

begin

val_ireq_tvalid<=1'b1;

val_ireq_tdata<=instruction;

val_ireq_tlast<=1'b1;

i<=i+1'b1;

end

19:

begin

val_ireq_tvalid<=1'b0;

val_ireq_tdata<=instruction;

val_ireq_tlast<=1'b1;

i<=i+1'b1;

end

default:

begin

val_ireq_tvalid<=1'b0;

val_ireq_tdata<=64'd0;

val_ireq_tlast<=1'b0;

end

endcase

end

else

begin

val_ireq_tvalid<=1'b0;

val_ireq_tdata<=64'd0;

val_ireq_tlast<=1'b0;

end

end

assign val_ireq_tuser = {8'h0,src_id,8'h0, dest_id};

assign val_ireq_tkeep=8'hff;

endmodule

顶层文件

module top(

input log_rst,

input sys_clkn,

input sys_clkp,

output srio_txn0,

output srio_txp0

);

wire [7:0] val_ireq_tkeep;

wire [31:0] val_ireq_tuser;

wire [63:0] val_ireq_tdata;

wire val_ireq_tvalid;

wire log_clk_out;

wire val_ireq_tready;

srio_nwrite_gen U1(

.log_clk(log_clk_out),

.log_rst(log_rst),

.val_ireq_tvalid(val_ireq_tvalid),

.val_ireq_tkeep(val_ireq_tkeep),

.val_ireq_tuser(val_ireq_tuser),

.val_ireq_tready(val_ireq_tready),

.val_ireq_tdata(val_ireq_tdata)

);

//wire srio_txn0;

//wire srio_txp0;

rio ip_rio(//调用的ip核

.log_clk_out(log_clk_out),

.s_axis_ireq_tdata(val_ireq_tdata),

.s_axis_ireq_tkeep(val_ireq_tkeep),

.s_axis_ireq_tvalid(val_ireq_tvalid),

.s_axis_ireq_tuser(val_ireq_tuser),

.s_axis_ireq_tready(val_ireq_tready),

.srio_txn0(srio_txn0),

.srio_txp0(srio_txp0),

.srio_rxn0(srio_txn0),

.srio_rxp0(srio_txp0),

.sys_clkn(sys_clkn),

.sys_clkp(sys_clkp),

.sys_rst(log_rst)

);

endmodule

添加的激励如下:

module sim(

input log_rst,

input sys_clkn,

input sys_clkp,

output srio_txn0,

output srio_txp0

);

top sim_top(

.log_rst(log_rst),

.sys_clkn(sys_clkn),

.sys_clkp(sys_clkp),

.srio_txn0(srio_txn0),

.srio_txp0(srio_txp0)

);

reg sys_clkp_reg;

initial begin

sys_clkp_reg = 1'b0;

forever #40 sys_clkp_reg = ~sys_clkp_reg;

end

assign sys_clkn = ~sys_clkp_reg;

assign sys_clkp=sys_clkp_reg;

// reset generator

reg log_rst_reg;

initial begin

log_rst_reg = 1'b1;

#1000

log_rst_reg = 1'b0;

end

assign log_rst=log_rst_reg;

endmodule

RTL图示如下,很简单:做的是回环测试:

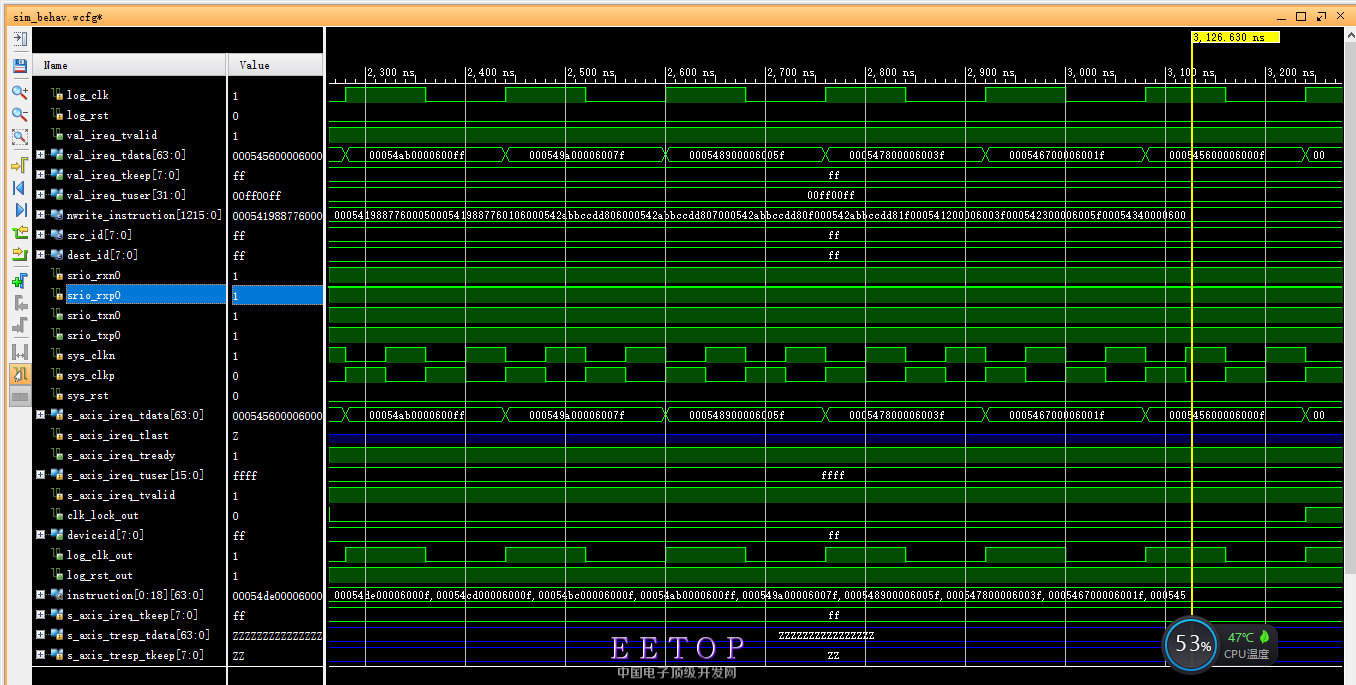

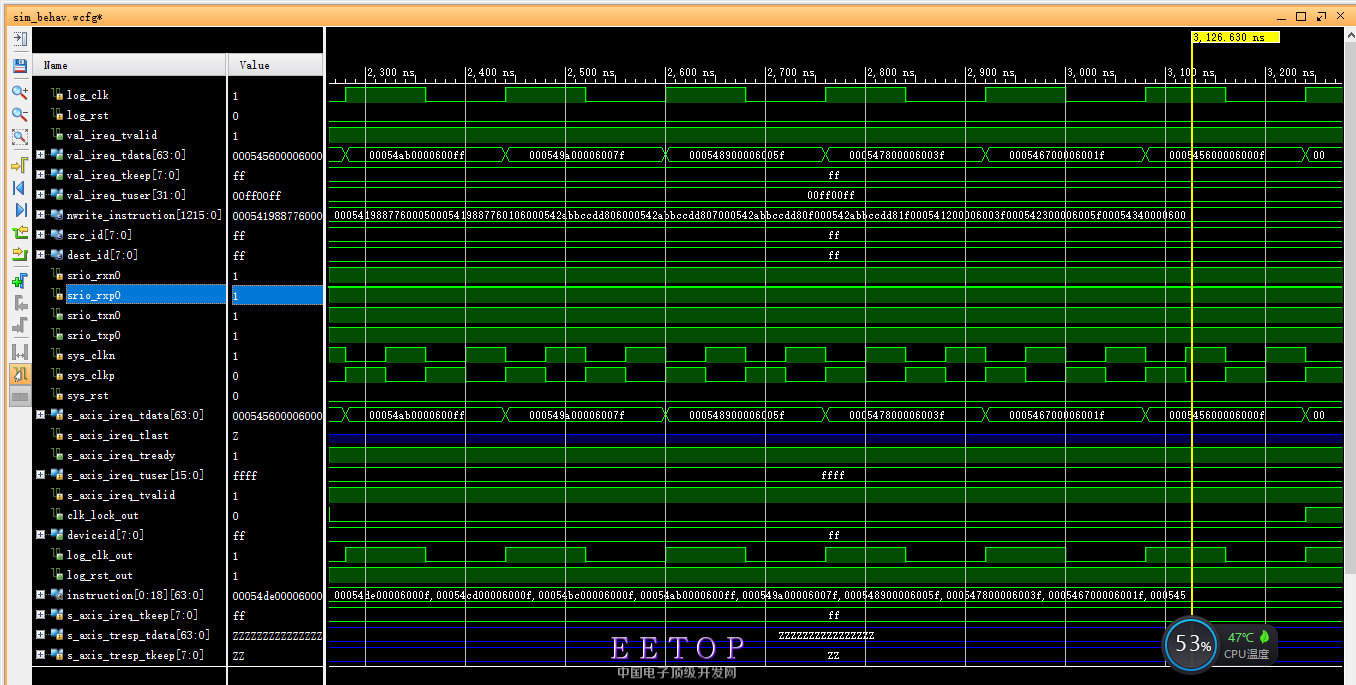

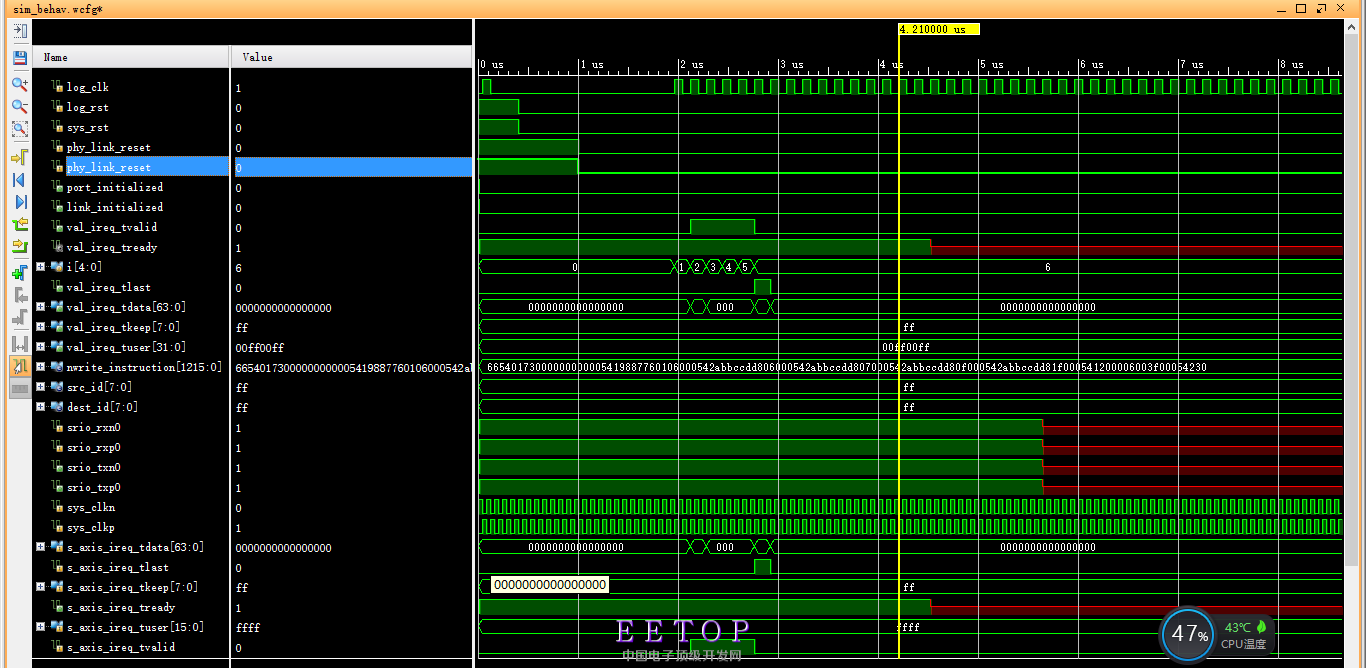

仿真图片如下:问题也很明显了,就是srio_txp0,srio_txp0,srio_rxn0,srio_rxp0始终保持高电平,就是没没有传输成功。

问题到底出在哪里了,跪求大神的解答,真是没有办法了,就是搞不定,也没地方去问,百度一下,翻了几十页都没有实例解说,真是把我搞得一点信心都没有了,真心希望智者给解答一下,感激不尽。

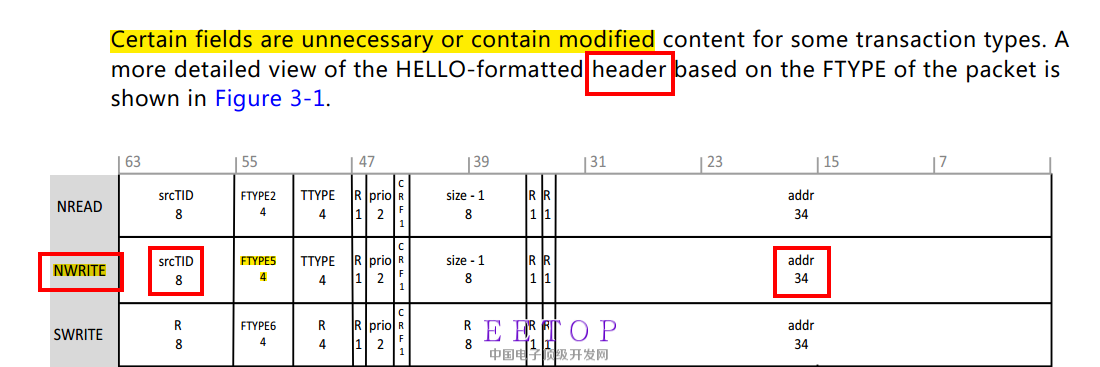

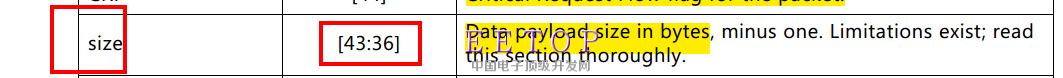

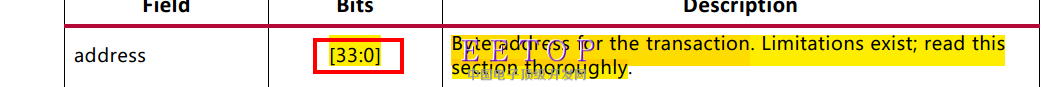

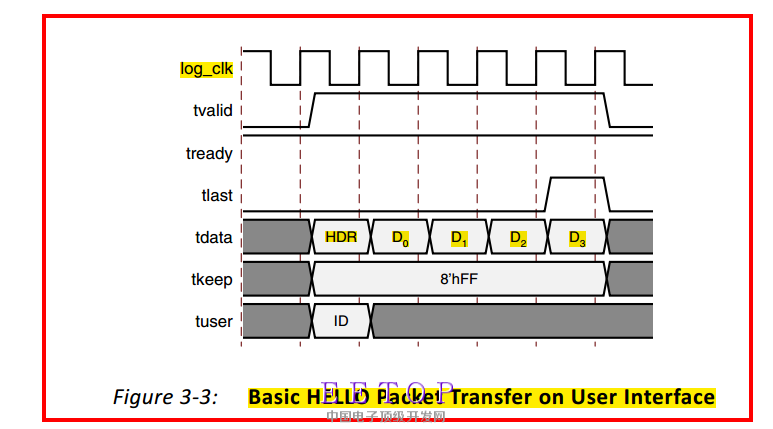

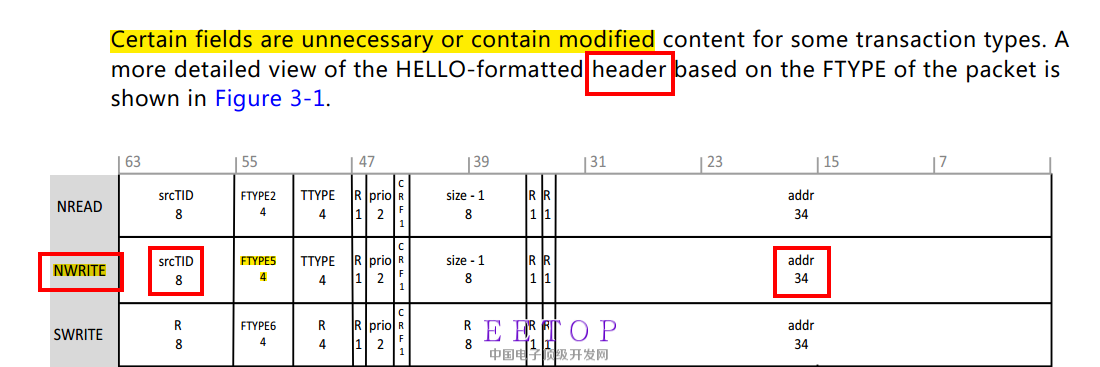

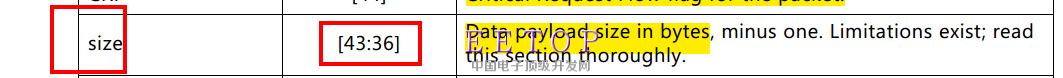

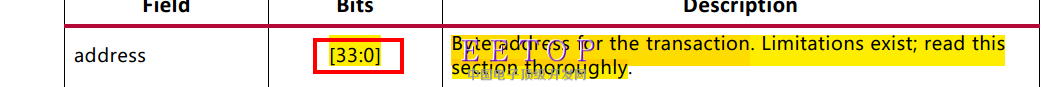

看看这两张图,我们这里只看NWRITE这种传输格式:tdata首先是发送一个包头header,他是64位的,这个包头里包含了很多信息,我们只看size 和addr部分,

Figure 3-3 shows a typical transfer with data on one of the user interface ports. This

particular transfer has a data payload of four DWORDs (32 bytes). On the interface, it takes

five total cycles including the transfer of the header.

假设传输4个字节(32bytes),就是第一张图,说明书就是这么说的。我纳闷的地方出来了:

1.包头给了个地址,没问题,最终传给目的地的时候,按给出的地址写进去数据D0,但是D1,D2,D3的地址可怎么处理啊。

2.假设传输4个字节,tdata是64位啊,每个时钟可怎么给tdata输入D0,D1,D2,D3,四个数据啊,每个只有8bytes,却要填进64位的tdata,还是说数据量太小,只能造成浪费。

3.size到底是什么意思?最大是设置成256个bytes,假设就设置成了255,过了包头之后,每来一个时钟,按照上图,传送8个字节,需要走32个时钟,才能传完256个字节,这不是浪费了tdata这个64位的接口了吗?只是header用的到64位,之后只用8位。还是说就是这样的,我的理解是正确的。

我的疑问是link_initialized还有port_initialized始终都都无法变为1,这是为什么呢?究竟怎样操作才能使他变为1,不变1不能进行数据传输,看我上传的图片。phy_link_reset没有将link_initialized变为1,抓狂中。

这是一个模块

module srio_nwrite_gen(

input log_clk,

input log_rst,

input val_ireq_tready,

// input [15:0] src_id,

// input [15:0] dest_id,

// input [15:0] source_id,

output reg val_ireq_tvalid,

// input val_ireq_tready,

// output reg val_ireq_tlast,

output reg [63:0] val_ireq_tdata,

output [7:0] val_ireq_tkeep,

output [31:0] val_ireq_tuser

);

localparam [7:0] src_id=8'hff;

localparam [7:0] dest_id=8'hff;

localparam [3:0] NWRITE=4'd5;

localparam [3:0] TNWR =4'd4;

localparam [64*19-1:0] nwrite_instruction = {

// NWRITEs

{12'h000, NWRITE, TNWR, 36'h198877600, 8'd5},

{12'h000, NWRITE, TNWR, 36'h198877601, 8'd6},

{12'h000, NWRITE, TNWR, 36'h2ABBCCDD8, 8'd6},

{12'h000, NWRITE, TNWR, 36'h2ABBCCDD8, 8'd7},

{12'h000, NWRITE, TNWR, 36'h2ABBCCDD8, 8'd15},

{12'h000, NWRITE, TNWR, 36'h2ABBCCDD8, 8'd31},

{12'h000, NWRITE, TNWR, 36'h120000600, 8'd63},

{12'h000, NWRITE, TNWR, 36'h230000600, 8'd95},

{12'h000, NWRITE, TNWR, 36'h340000600, 8'd127},

{12'h000, NWRITE, TNWR, 36'h450000600, 8'd255},

{12'h000, NWRITE, TNWR, 36'h560000600, 8'd15},

{12'h000, NWRITE, TNWR, 36'h670000600, 8'd31},

{12'h000, NWRITE, TNWR, 36'h780000600, 8'd63},

{12'h000, NWRITE, TNWR, 36'h890000600, 8'd95},

{12'h000, NWRITE, TNWR, 36'h9A0000600, 8'd127},

{12'h000, NWRITE, TNWR, 36'hAB0000600, 8'd255},

{12'h000, NWRITE, TNWR, 36'hBC0000600, 8'd15},

{12'h000, NWRITE, TNWR, 36'hCD0000600, 8'd15},

{12'h000, NWRITE, TNWR, 36'hDE0000600, 8'd15}};

wire [63:0] instruction[0:18];

genvar ii;

generate

for (ii = 0; ii <19; ii = ii + 1) begin : instruction_gen

assign instruction[ii] = nwrite_instruction[(ii+1)*64-1:ii*64];

end

endgenerate

reg [4:0] i;

reg val_ireq_tlast;

always @(posedge log_clk or negedge log_rst)

if(log_rst)

begin

val_ireq_tvalid<=1'b0;

val_ireq_tdata<=64'd0;

val_ireq_tlast<=1'b0;

i<=4'd0;

end

else

begin

if(val_ireq_tready)

begin

case(i)

0,1,2,3,4,5,6,7,8,9,10,11,12,13,14,15,16,17:

begin

val_ireq_tvalid<=1'b1;

val_ireq_tdata<=instruction;

val_ireq_tlast<=1'b0;

i<=i+1'b1;

end

18:

begin

val_ireq_tvalid<=1'b1;

val_ireq_tdata<=instruction;

val_ireq_tlast<=1'b1;

i<=i+1'b1;

end

19:

begin

val_ireq_tvalid<=1'b0;

val_ireq_tdata<=instruction;

val_ireq_tlast<=1'b1;

i<=i+1'b1;

end

default:

begin

val_ireq_tvalid<=1'b0;

val_ireq_tdata<=64'd0;

val_ireq_tlast<=1'b0;

end

endcase

end

else

begin

val_ireq_tvalid<=1'b0;

val_ireq_tdata<=64'd0;

val_ireq_tlast<=1'b0;

end

end

assign val_ireq_tuser = {8'h0,src_id,8'h0, dest_id};

assign val_ireq_tkeep=8'hff;

endmodule

顶层文件

module top(

input log_rst,

input sys_clkn,

input sys_clkp,

output srio_txn0,

output srio_txp0

);

wire [7:0] val_ireq_tkeep;

wire [31:0] val_ireq_tuser;

wire [63:0] val_ireq_tdata;

wire val_ireq_tvalid;

wire log_clk_out;

wire val_ireq_tready;

srio_nwrite_gen U1(

.log_clk(log_clk_out),

.log_rst(log_rst),

.val_ireq_tvalid(val_ireq_tvalid),

.val_ireq_tkeep(val_ireq_tkeep),

.val_ireq_tuser(val_ireq_tuser),

.val_ireq_tready(val_ireq_tready),

.val_ireq_tdata(val_ireq_tdata)

);

//wire srio_txn0;

//wire srio_txp0;

rio ip_rio(//调用的ip核

.log_clk_out(log_clk_out),

.s_axis_ireq_tdata(val_ireq_tdata),

.s_axis_ireq_tkeep(val_ireq_tkeep),

.s_axis_ireq_tvalid(val_ireq_tvalid),

.s_axis_ireq_tuser(val_ireq_tuser),

.s_axis_ireq_tready(val_ireq_tready),

.srio_txn0(srio_txn0),

.srio_txp0(srio_txp0),

.srio_rxn0(srio_txn0),

.srio_rxp0(srio_txp0),

.sys_clkn(sys_clkn),

.sys_clkp(sys_clkp),

.sys_rst(log_rst)

);

endmodule

添加的激励如下:

module sim(

input log_rst,

input sys_clkn,

input sys_clkp,

output srio_txn0,

output srio_txp0

);

top sim_top(

.log_rst(log_rst),

.sys_clkn(sys_clkn),

.sys_clkp(sys_clkp),

.srio_txn0(srio_txn0),

.srio_txp0(srio_txp0)

);

reg sys_clkp_reg;

initial begin

sys_clkp_reg = 1'b0;

forever #40 sys_clkp_reg = ~sys_clkp_reg;

end

assign sys_clkn = ~sys_clkp_reg;

assign sys_clkp=sys_clkp_reg;

// reset generator

reg log_rst_reg;

initial begin

log_rst_reg = 1'b1;

#1000

log_rst_reg = 1'b0;

end

assign log_rst=log_rst_reg;

endmodule

RTL图示如下,很简单:做的是回环测试:

仿真图片如下:问题也很明显了,就是srio_txp0,srio_txp0,srio_rxn0,srio_rxp0始终保持高电平,就是没没有传输成功。

问题到底出在哪里了,跪求大神的解答,真是没有办法了,就是搞不定,也没地方去问,百度一下,翻了几十页都没有实例解说,真是把我搞得一点信心都没有了,真心希望智者给解答一下,感激不尽。

看个简单的问题吧,上面的内容可能不愿意看,大家来看一个更简单的吧:

看看这两张图,我们这里只看NWRITE这种传输格式:tdata首先是发送一个包头header,他是64位的,这个包头里包含了很多信息,我们只看size 和addr部分,

Figure 3-3 shows a typical transfer with data on one of the user interface ports. This

particular transfer has a data payload of four DWORDs (32 bytes). On the interface, it takes

five total cycles including the transfer of the header.

假设传输4个字节(32bytes),就是第一张图,说明书就是这么说的。我纳闷的地方出来了:

1.包头给了个地址,没问题,最终传给目的地的时候,按给出的地址写进去数据D0,但是D1,D2,D3的地址可怎么处理啊。

2.假设传输4个字节,tdata是64位啊,每个时钟可怎么给tdata输入D0,D1,D2,D3,四个数据啊,每个只有8bytes,却要填进64位的tdata,还是说数据量太小,只能造成浪费。

3.size到底是什么意思?最大是设置成256个bytes,假设就设置成了255,过了包头之后,每来一个时钟,按照上图,传送8个字节,需要走32个时钟,才能传完256个字节,这不是浪费了tdata这个64位的接口了吗?只是header用的到64位,之后只用8位。还是说就是这样的,我的理解是正确的。

你的serders都没有正常工作

你的clk_lock_out中间是低的,会不会是没初始化成功?

查看了一下,确实是link_initialized 还有port_initialized两个输出端口始终保持为0,就是没有初始化成功。原先以为,置位sys_clk一段时间,在清零之后就可以完成ip核的初始化。那么究竟怎样进行初始化呢?

我做过

这个要多等一段时间 我在modelsim上仿的时候 大概要到1300us?左右才会初始化成功

总之 要很长时间才行

[img][/img]

我的疑问是link_initialized还有port_initialized始终都都无法变为1,这是为什么呢?究竟怎样操作才能使他变为1,不变1不能进行数据传输,看我上传的图片。phy_link_reset没有将link_initialized变为1,抓狂中。

您做过,千万教教我啊,您要是不教我,那就是在我的心口上扎刀子啊。前辈请指点一二,在我眼前的是重重迷雾,看不到srio的本质,您赐教啊。

您能说的再清楚一点吗?srio中会嵌有serdes吗,您的意思是并转串并没有实现,也就是txp,txn没有数值,您觉得是什么问题呢?期待您的指教。

请问有srio的license吗?无法生成bit文件啊

没有。

我是来水贴的,不好意思哈

我也很困惑,srio的使用越来越广泛,但是这个IP核是收费的,而且费用非常高,很令人生气,难道用的人都要买吗,真是蛋疼。