关于Quartus的FIFO IP核时序设计问题

时间:10-02

整理:3721RD

点击:

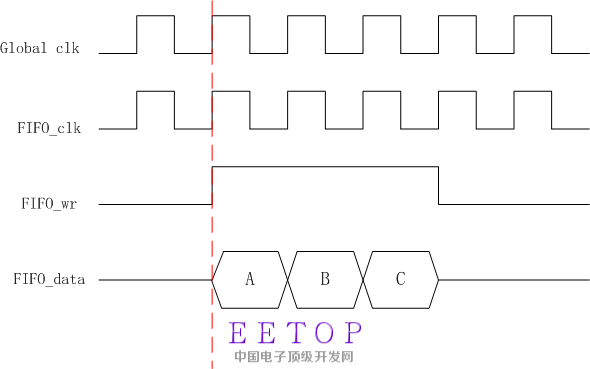

在实际设计中,有个模块控制FIFO写入数据A,假设全局时钟global_clk以时序逻辑的方式驱动FIFO的写使能(fifo_wr)和写数据(data),而FIFO的时钟信号就直接赋上global_clk,那么就会得到如图1所示的时序图。

写使能和数据都在global_clk上升沿发生变化。

那么问题就来了,按道理说,FIFO写入数据是在wr拉高前提下,在fifo_clk上升沿写入数据。那么是不是这样设计就不满足数据的保持时间?

换一种设计,FIFO的写使能(fifo_wr)和写数据(data)依然基于global_clk的时序逻辑,但是fifo_clk相对于global_clk有个相移,比如说反相。那么就得到了图2的时序图,这样就满足设计需求了吗?

我想请问的是,一般工程设计,怎样设计FIFO的时序(主要是时钟吧)是怎样的呢?

1、如果只写一个数据,写使能只能有效一拍

2、当前时钟沿有效写使能和数据,是在下一个时钟沿写入数据的

画图的时候不严谨,重新修改了一下。你的2,我理解的是第一个FIFO_clk上升沿有效写使能和数据,但是此时FIFO_clk上升沿下,写使能和数据都在处于变换阶段,处于建立时间状态。难道不会存在不稳定情况下吗?

最好别按照第二个方法来。 按照第一个方式。 注意,图一中,fifo不是在第一个红线处采你写入的数据的,是在下一拍采的。

同步设计,施加适当的时序约束,且涉及满足时序约束,不存在不稳定的状态

但是我的数据A在第二个时钟上升沿到来时,恰好变换为数据B,这个时候会有问题吗?

工程中用到很多FIFO做缓存,那么所有的FIFO时钟都要添加时序约束吗?