关于Kintex-7的IODELAY的使用问题

时间:10-02

整理:3721RD

点击:

[i=s] 本帖最后由 REDARMY007 于 2017-6-25 22:34 编辑 [/i]

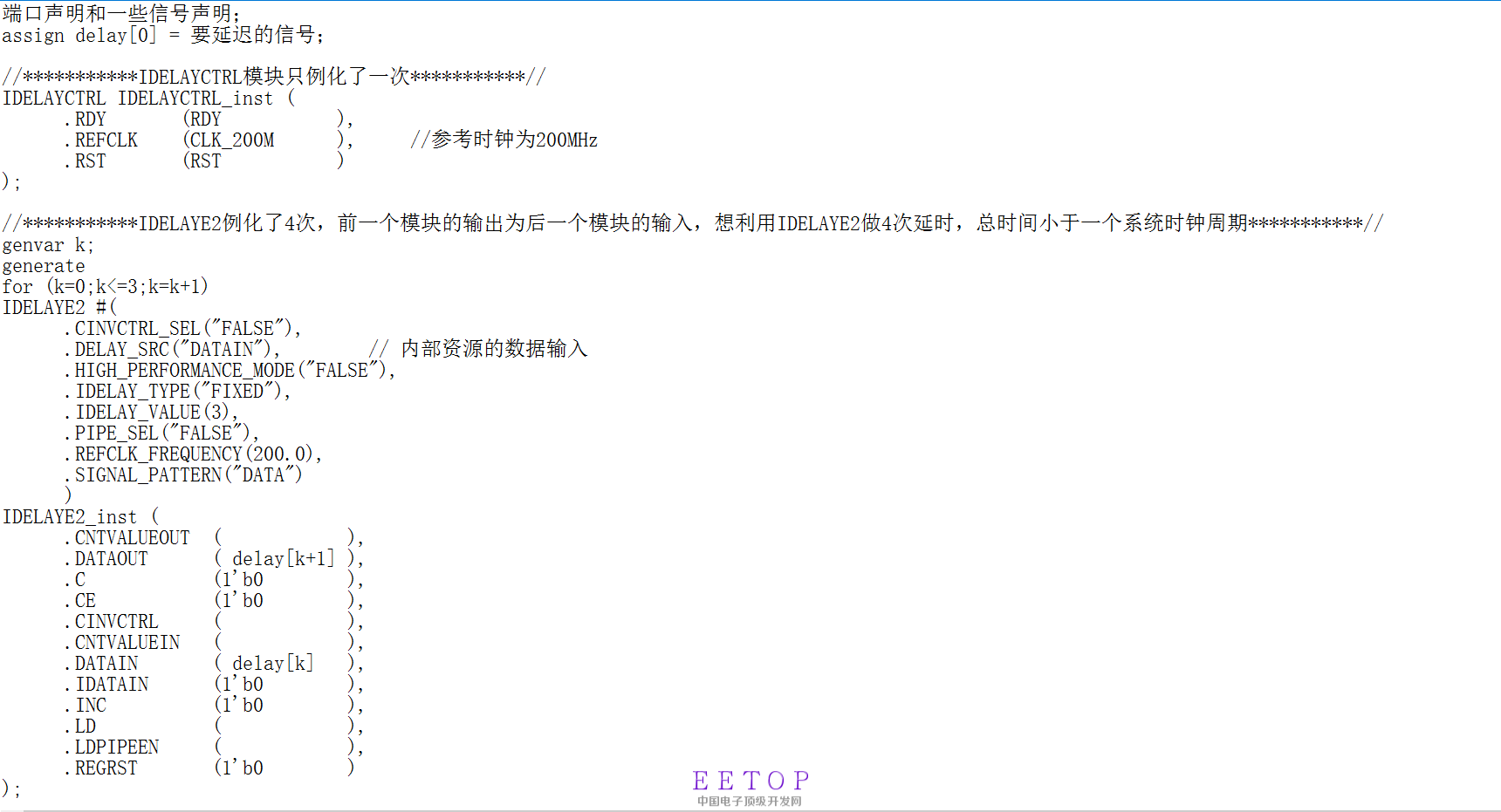

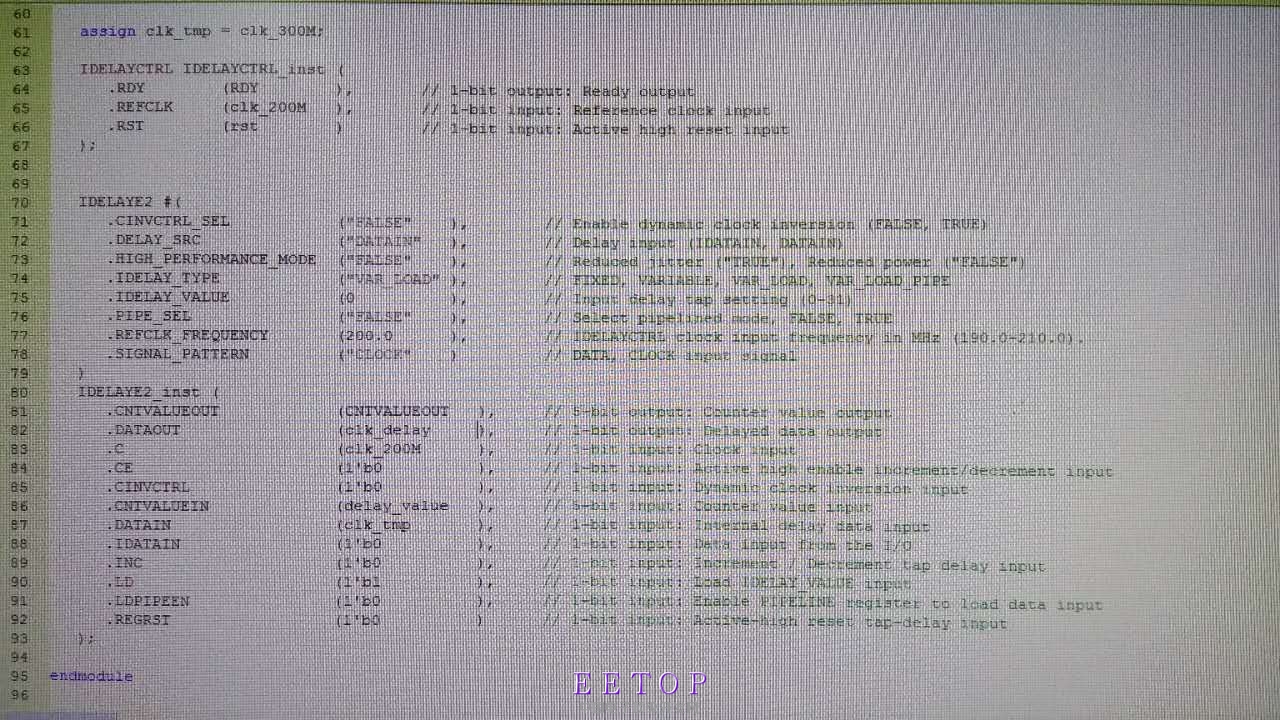

最近正在使用K7的IODELAY模块,想利用IODELAY模块实现小于一个系统时钟的延时,代码如下:

最近正在使用K7的IODELAY模块,想利用IODELAY模块实现小于一个系统时钟的延时,代码如下:

注意IDELAY的输入,DATAIN和IDATAIN是不一样的,具体去看手册吧。

另外从你代码上看,delay[1]是delay[0]的延迟产生的,delay[2]又是delay[1]产生的,我没有这么用过,不知道内部的走线能不能走通。然后你又从这一堆delay里面选出来一个,为什么这么做呢?控制idelay的延迟tap,可以达到同样的功能。首先你这个是想用多个IODELAY做循环延时,串起来。的确这种用法很少见,不过并没有发现明显的问题。

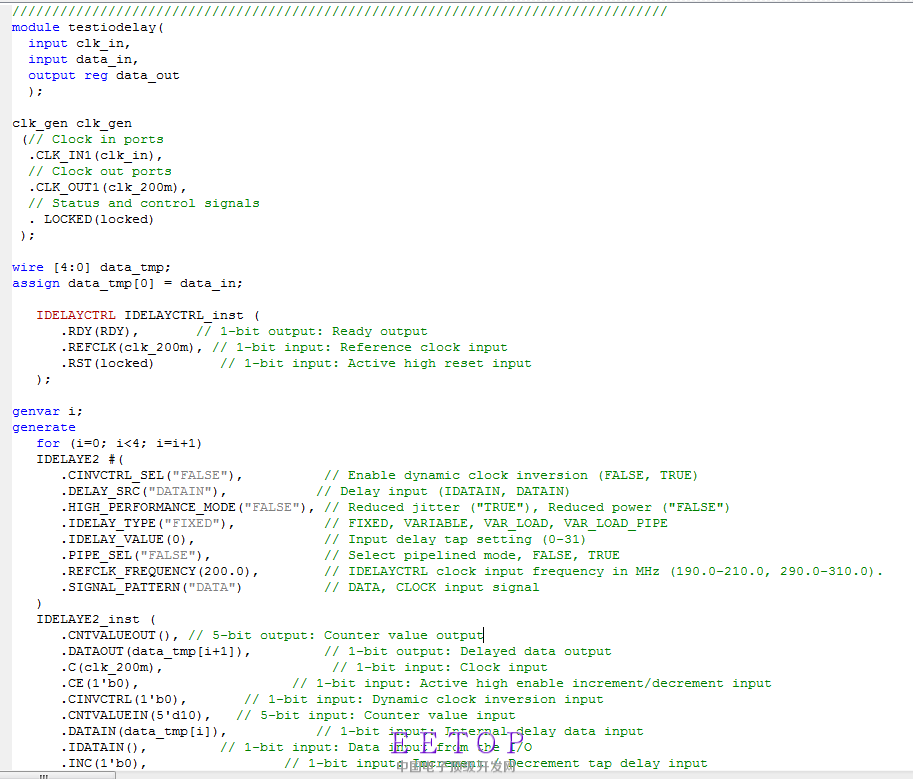

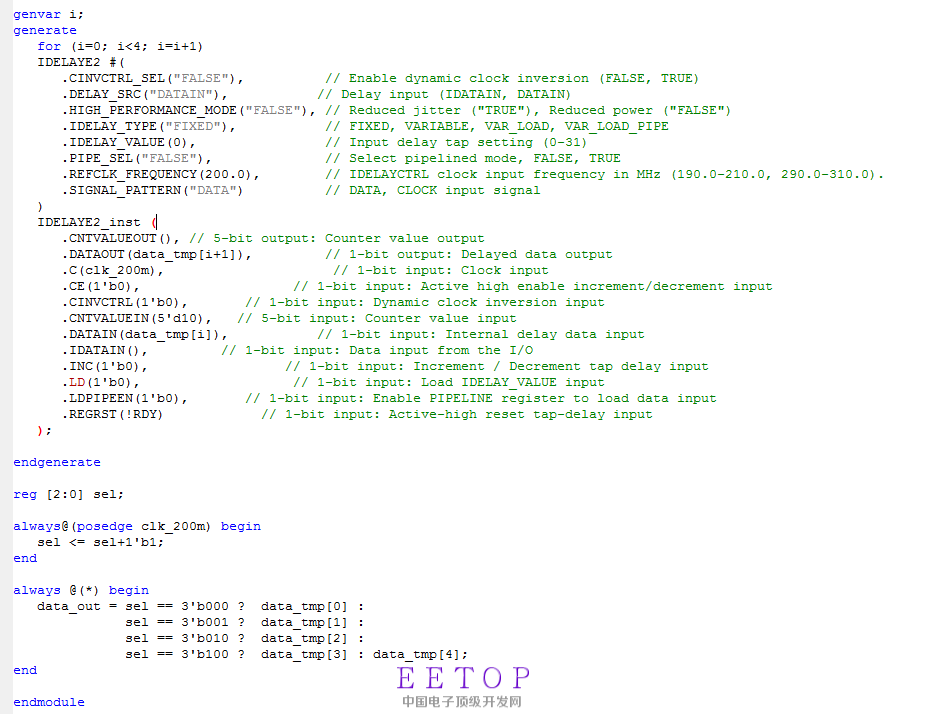

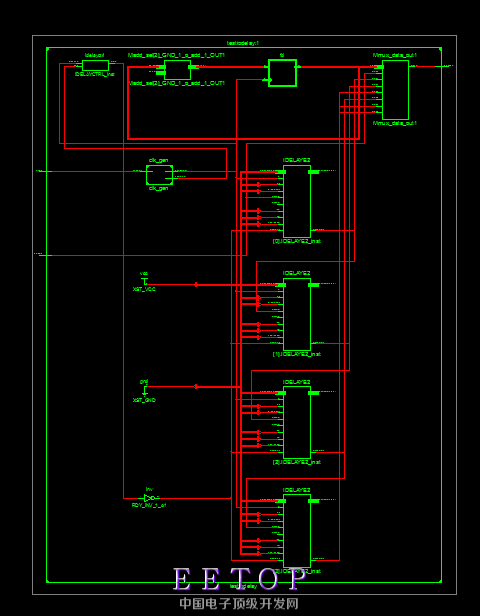

于是按照你的意思,我做了一个小实验。

如下所示:

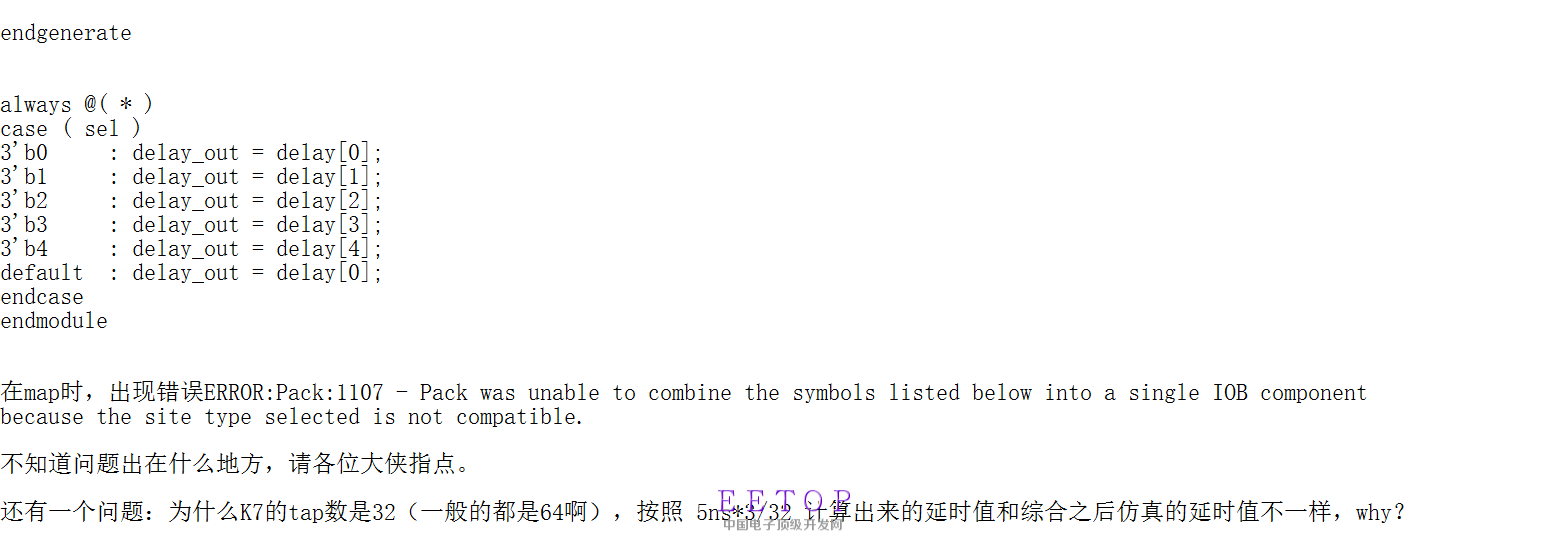

ISE视乎也正确的识别了你的意图,然后,bit文件正确生成。

所以.........

IODELAY的输入有两种一种是DATAIN,另一种是IDATAIN,你这个有的输入时IBUF有的是内部资源,我觉得是这个错误,你可以试试,在输入端加入IBUF,在输入给IODELAY模块

根据这个代码rouat,发现clk_in,没有接到pll上谢谢大家的建议。重新看了下IDELAYE2的手册,将代码修改了下,没再出问题,如下图,

接下来就是IDELAYCTRL的LOC约束,INST "instance_name" LOC = IDELAYCTRL_X#Y#;中的X#Y#怎么确定?

由于idelay这种模块,起控制延时的作用。所以工具选择将你使用的idelay布到哪个地方很重要,可能会影响延时的数值。如果你的输入是io的话,那就不用约束,工具会使用相应的IOB里面的idelay。像你这种用法呢,可以先调试,先跑出来一个工程,然后打开看下它的位置,再加到约束里面去。

如果需要延时的信号是从芯片管脚输入的,那么综合时会报错,你只需将它提示的IDELAYCTRL位置加入到约束文件中就行了。如果是内部信号延时,就按照楼上的说法做,不过最好将4个IDELAYE2也进行约束,位置靠近。这样误差小。貌似小编一楼的用法也没有错。当然前提是你给delay[0]的那个要延迟的信号不是从芯片管脚输入的。

多谢了,学习中

学FPGA,来至芯科技!111