如何用Design Compiler查看元件库中的元件信息?

时间:10-02

整理:3721RD

点击:

因为我很少接触ASIC上的设计,这问题应该属于新手小白问题......

我们在设计中需要用到一个选通双输入的寄存器。从设计要求上,希望所占的面积(或者说等效门数,GE)尽可能小。之前都是直接把设计的Verilog代码放到DC里compile,然后report area。我现在用的是TSMC180的library,输出的实现是一个MUX+一个DFF,整体的面积偏大。

今天看到有论文说,这种功能可以用scan-flip-flop来代替,在很多library里会更小。

主要问题有两个:

1、现在没有设计,如何从元件库里得到这种部件的面积(等效门数)?

2、如果SCAN-FF确实更好,如何使得DC优先使用SCAN-FF?如果直接在代码里干预,会不会使得RTL代码变得不可移植,不能用于其他的library?

我们在设计中需要用到一个选通双输入的寄存器。从设计要求上,希望所占的面积(或者说等效门数,GE)尽可能小。之前都是直接把设计的Verilog代码放到DC里compile,然后report area。我现在用的是TSMC180的library,输出的实现是一个MUX+一个DFF,整体的面积偏大。

今天看到有论文说,这种功能可以用scan-flip-flop来代替,在很多library里会更小。

主要问题有两个:

1、现在没有设计,如何从元件库里得到这种部件的面积(等效门数)?

2、如果SCAN-FF确实更好,如何使得DC优先使用SCAN-FF?如果直接在代码里干预,会不会使得RTL代码变得不可移植,不能用于其他的library?

1、现在没有设计,如何从元件库里得到这种部件的面积(等效门数)?

-->每一个library都会有一个standard cell的文档,里面有每个cell的时序和面积等信息

2、如果SCAN-FF确实更好,如何使得DC优先使用SCAN-FF?如果直接在代码里干预,会不会使得RTL代码变得不可移植,不能用于其他的library?

-->SCAN-FF一般是自动插入的,在compile_ultra时加-scan的选项

多谢!面积我查到了,确实是SCAN_FF小一点。

还想请教一下,compile scan这样能将原来的MUX+DFF换成SCAN_FF吗?跟一般的应用不同,我这里不是想要用扫描链做测试,只是单纯的想用SCAN_FF代替MUX+DFF而已。实际上是希望把寄存器置初值的输入端做成SCAN_FF的SI,可以不用加MUX了。这样compile是不是只能把DFF都换成SCAN_FF,原有的MUX还是MUX?

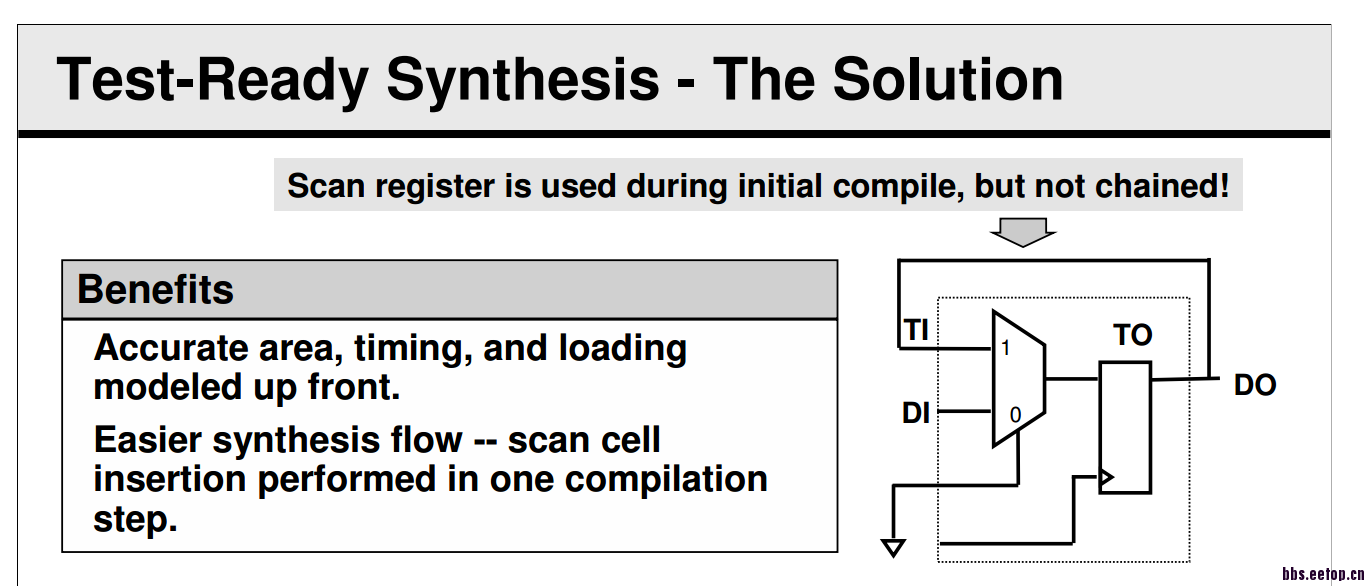

是的,上图

great info

可以考虑改改scan_ff的属性,在.lib中改。综合时因该会自动选择面积小的。如果没有自动选择,因该有命令可以指定。

没有实际操作过,只是个人的一点想法。

这样compile是不是只能把DFF都换成SCAN_FF,原有的MUX还是MUX?

--是的。直接用compile -scan会出现上述结果。

可以尝试把SCAN_FF的.lib文件的scan属性改了,改成普通单元,再用compile,也许会自动选用SCAN_FF。

记得不是很清楚了,DC中好像有命令可以直接指定单元类型。

太棒了