modelsim仿真与实际功能不符问题?

1.问题描述:从modelsim仿真图上看,标志信号没有被正确的采样到,但是该标志信号控制的信号却能够正确的执行。

以位计数器(bit_cnt)为例,相关verilog代码如下

always @(posedge MCLK or negedge rst)

if(~rst)begin

sck_r3 <= 1'b 0;

sck_r2 <= 1'b 0;

sck_r1 <= 1'b 0;

end

else if(RESET | reset_DRDY)begin

sck_r3 <= 1'b 0;

sck_r2 <= 1'b 0;

sck_r1 <= 1'b 0;

end

else

begin

sck_r3 <= sck_r2; // synchronizers

sck_r2 <= sck_r1; // synchronizers

sck_r1 <= sck ^ pol; // select the desired polarity ofthe slave clk

end

assign shift_clk_negedge = ~(sck ^ pol) & sck_r1; //pol= 0, SCK's negedge;pol = 1, SCK's posedge

assign shift_clk_negedge_1 = ~sck_r1 & sck_r2;

always @(posedge MCLK or negedge rst)

if(~rst)

bit_cnt <= 3'b 111;

else if(spi_state == idle)

bit_cnt <= 3'b 111;

else if(shift_clk_negedge == 1'b 1)

bit_cnt <= bit_cnt - 3'h 1;

pol信号固定为1,shift_clk_negedge和shift_clk_negedge_1信号为sck上升沿指示信号,高电平有效。bit_cnt应该是在MCLK的上升沿并且shift_clk_negedge为1时,才会进行减1操作。

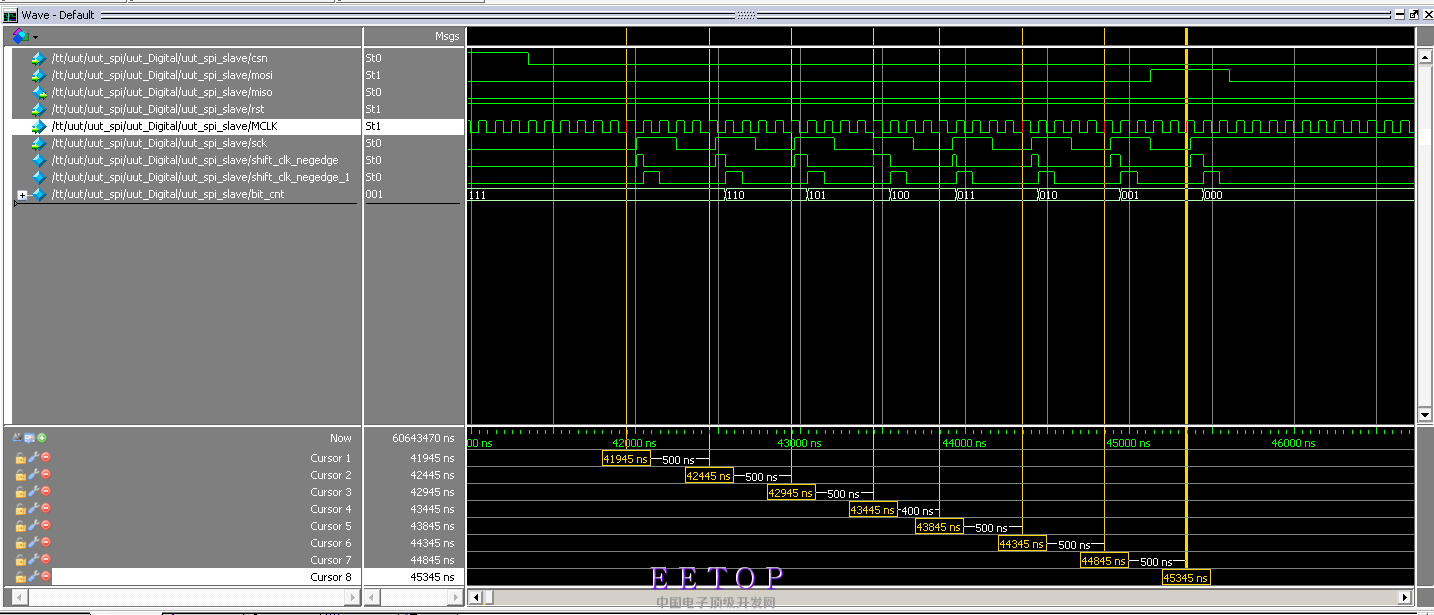

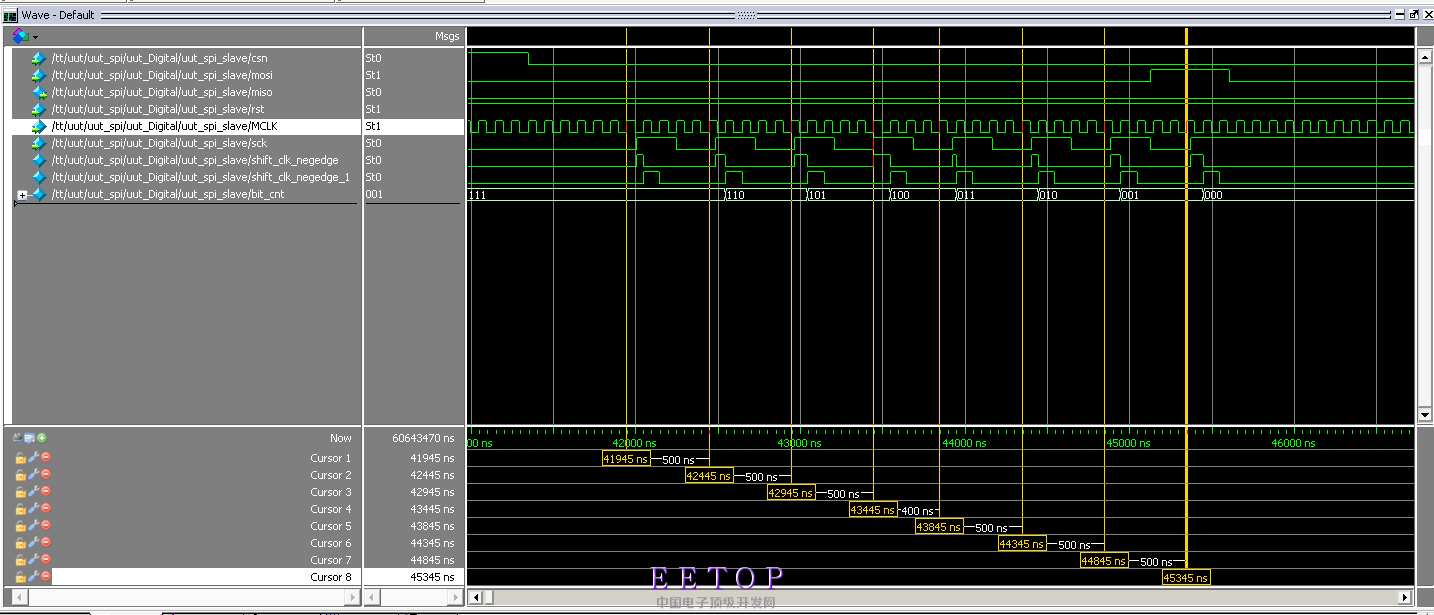

Modelsim仿真图如下(前仿真):

从该图上可以看出,仅有第四根黄线部分采样到shift_clk_negedge信号为1,其他地方都未采样到,但是bit_cnt却进行了减1操作。但是第一根黄线这里,没有采样到shift_clk_negedge信号为1,也没有进行减1操作。源文件,仿真文件和仿真设置都没有问题。

该问题产生的原因是什么?为何与verilog描述的功能不符合?

1、第一个bit_cnt没有减1的可能,是不是spi_state还处于idle?这个信号能否拉出来看看?

2、第一个negedge是两个异步信号产生的结果,是否可以把第二个always里面判断negedge==1换成negedge_1==1,negedge_1是两个同步信号产生的结果,也许波形上看着更好分析。不知道你设计的意图是否可以允许这样?感觉这个问题也许是受到<=赋值的同一个时钟边沿的各种event区域处理的先后顺序所致,不过暂时没有分析出结果。你也可以根据这个思路去考虑一下。总觉得直接异步过来的信号,拿来做判断可能是有风险的。

首先谢谢你的回复,由于这版设计,已经流片了,所以我就只能从代码角度分析哪里可能会出现问题。你刚刚提到的这个,确实是准备用这个negedge—1信号去做。目前芯片不知道会不会出现和波形图一样的这种采样问题。如果说,各个信号与时钟信号到来的时间不一致,会不会出现问题,导致芯片功能不正常。我现在就遇到对方公司表示,读数据不对,一直在分析原因。

画电路图出来再认真分析比较好点,看看你的代码表达的意思是否和电路图一致。

反正我是觉得采集第一个negedge存在风险,是异步的。

sck_r2 ,sck_r3去做上/下沿有效信号,你这个用异步信号直接做逻辑,回来片子肯定废了,现在spi还要自己去写?

我也认为用异步信号不好,不过这是上一届设计的,我和导师说这个地方有风险,他不让我改

片子是有问题,好像数字后端没做好还是咋滴,不太清楚。那你们工作时,像SPI,IIC这种接口一般是怎么办呢?

仿真的结果是对的,是你理解错了

第二根黄线和第三根黄线后面的时钟沿都采到了shift_clk_negedge为1

第四根黄线也是在黄线后的那个时钟沿采到的shift_clk_negedge

这个地方其实我确认过,在黄线的下一个时钟沿如果采样到该信号为1,计数器依旧会减一对吧?不过在黄线后面的下一个主时钟上升沿,该信号为0,所以应该不会减一,还有一点就是,如果是这个时钟采样到该信号为1,bit_cnt的跳变也应该在下一个主时钟的上升沿那里才对吧?

希望你能把我的错误指出来,我一直没想明白

黄线处并没有采到 1 ; 黄线后的那个时钟沿才采到,cnt是D触发器,所以它的值在黄线后的那个时钟沿就立即变了

仿真的结果是对的

首先很谢谢你的指导,让我发现了自己对基础知识理解的一些错误,不过我还有个问题想问你。1.黄线后一个周期的时钟上升沿,该信号是由1跳变到0,我在modelsim上把线弄到时钟上升沿,该信号处显示为0,这里我应该把该信号看成1还是0。2.你说的这个cnt是D触发器,所以cnt在时钟沿的时候立即跳变。这里不是很明白,我一直认为,D触发器具有延时一个周期的功能?不知道我的理解对不对?

1. 因为你的edge信号实在时钟控制下产生的,所以他的变化比时钟沿有一个很小的延时,但是这个延时你在modesim做前仿是看不到的。你看到的edge的变化跟是种沿是对其的,再加上下一个触发器采这个信号的时候需要一定的建立时间所以在黄线处是采不到的。

2,D触发器的延时作用产生的原因同1

你好,我还是没有明白这个仿真结果为什么会是对的,总感觉应该是前一个时钟采样到条件满足,下一个时钟数据才更新,不知道是不是我对非阻塞赋值方式的理解有错误?希望你能为我解答疑惑

1.都采样到了信号的上升沿啊,但是不是和时钟同步的,你可以调出sck_r1和sck_r2的波形看一下

2.第一个边沿为啥不减1是不是因为你的spi_state还处于IDLE

第一个没有减一,我查看了一下那个时候的状态并不是出于idle,你说的都采样到了上升沿,我不太明白是什么意思?

不过肯定都采样到了sck的上升沿,但是图中黄线部分都没有采样到shift_clk_negedge为1 ,而是在下一个时钟沿采样到其为1。但是这个采样不是我最大的疑惑。

我最大的疑惑在于,为什么非阻塞赋值,这个计数器变量的更新没有延时一个周期。我的理解是当前时钟沿采样到条件满足,下一个时钟沿变量才更新?而图中的现象和我理解的完全不同。殷工所说的,因为cnt是D触发器,所以值会立即更新。

我的意思是被采样信号上升沿都采样到了,用这种打节拍的方法采样信号上升沿肯定有延时的,一般是一个时钟节拍的延时,至于减1应该就是和仿真的一样,你想寄存器的时钟有效沿来了之后,然后此时赋值的条件又是满足的,寄存器的数据不就更新了吗,其实应该有一个寄存器的传播延时,但是前仿真看不出来,你可以尝试写代码时候给寄存器加上一个估计的传播延时,看波形方便。 比如q<=#1 d;

哈哈,谢谢你,我已经明白了,其实是我对非阻塞赋值的理解有问题。你说的其实有一个时钟的延时,前仿真看不出来是什么意思?

非阻塞赋值应该是上升沿来之前的一刻就计算好相应变量的值,在上升沿来之后,就立即将刚刚计算好的值更新,不知道这样理解对不对?

我刚刚看错了,把寄存器的传播延时看成了,一个时钟的延时,传播延时应该就是说,第一个寄存器的D端到第二个寄存器Q端的延时,包括组合逻辑和线延时

传播延时是寄存器的延时,总的延时是包括线延时和器件延时的

非阻塞赋值应该是上升沿来之前的一刻就计算好相应变量的值,在上升沿来之后,就立即将刚刚计算好的值更新——对,大概就是这个意思。