FIFO ip最后一个数据会在下一个读出周期读出

你是不是贴个仿真波形图什么的好一点撒

确定写的时候,最后一个数写进去了?写信号能看到,不代表已经写进去了

你好,因为下一次读数,读出来的第一个就是前一次读数的最后一个数,所以我觉得应该是写入了。

写错了。

仔细检查读写操作,有没有写错,确认好。

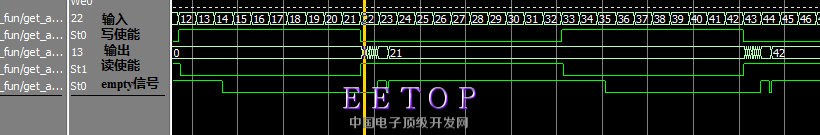

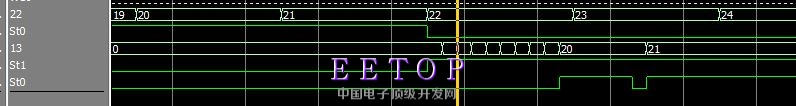

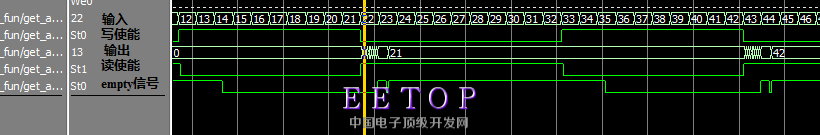

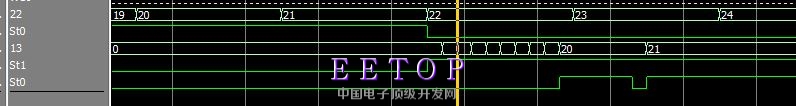

你好,我重新设定了读使能,但是,您看,它的读数为什么会这样,empty信号为什么在那有个变化。

你好,我重新设定了读使能,但是,您看,它的读数为什么会这样,empty信号为什么在那有个变化。

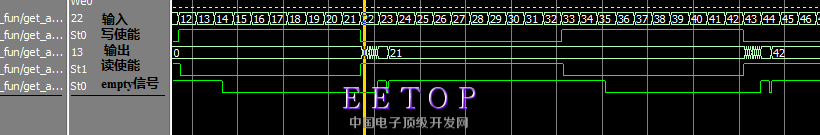

您好,这是放大了的图。

你好,我重新设定了读使能,但是,您看,它的读数为什么会这样,empty信号为什么在那有个变化。

最好把fifo所有的信号都看一下,最好空满标识都有。

读写使能都同步在一个时钟上?不是一个是5M,一个是50M,读之前应该判断一下empty。empty的变化原因应该是最后一个数据“21”还没写进去fifo,读使能就有效了。

http://bbs.eetop.cn/thread-385268-1-1.html

别人遇到相同的问题。

你看,你这个写了2个数以后,空信号才变成非空,说明写数据可能在入口有寄存器寄存,要不你拉长一下写使能,看出现什么现象?印象中,FIFO深度得是2的n次方啊,10不是啊

您说的对,FIFO的深度是2的n次方,因为我只需要10个数,所以就这么用了。我是个初学者,也不知道这样用对不对。

是的,我也觉得是这么个问题,改在empty后读使能生效就可以正常读了,我是个初学者,那怎么判断empty呢,我用的是计数器,写使能结束之后开始计数,计数到empty后开始读使能生效。

是的,我看到了,我现在觉得可能是数据没有完全写入,我就开始读了,所以会出现empty的那个问题。调整之后可以正常读出了。

好了,你明白问题的所在了。读写的时序问题,写有寄存器操作,消耗clk,造成读和写同时操作。

回复之后才看见帖子第二页问题已经解决了。所以把答案删除了

空指示信号在读时钟域生成,需要将写时钟域的地址同步到读时钟域,同步过程需要耗费几个写时钟周期的时间;

从这个图上可以看到,由于读写时钟相差较大,且读使能启动比较早,在最后一个写入数据的地址还没有完全同步到读时钟域前,在读时钟域,读地址就追上写地址了,因此空指示信号会拉高。