多时钟域问题,快时钟对慢时钟采样,设置不正确

时间:10-02

整理:3721RD

点击:

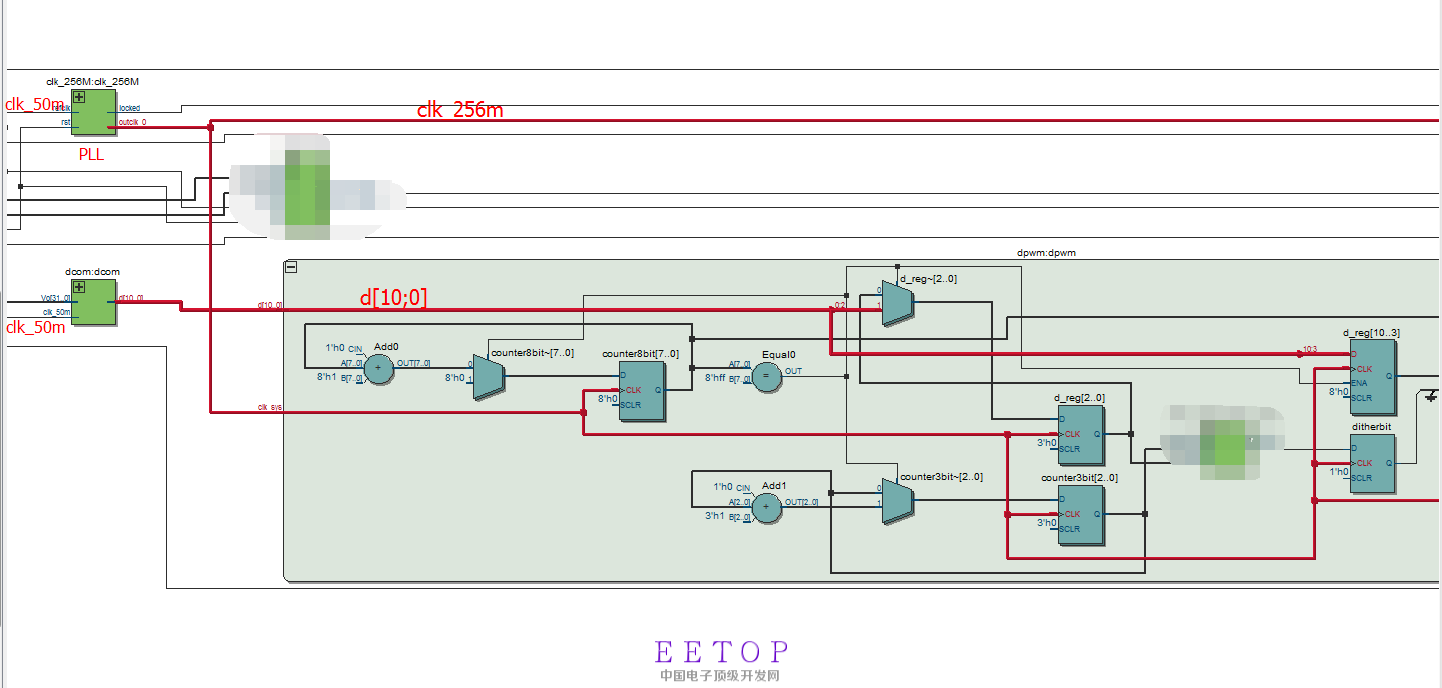

最近在做时钟综合,参考时钟50M,通过PLL 生成256M 时钟,然后 256M时钟接收50M时钟传输的数据,之前设置过set false path 、set group 、set_multicycle_path 为什么约束后没有改变。 请问该怎么设置?

点住错误的路径,右键选set false path

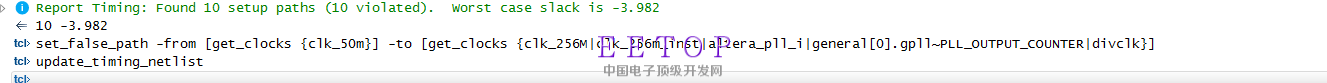

我试了一下set false path between nodes 和 clock ,结果都不顶用。为什么约束不住?

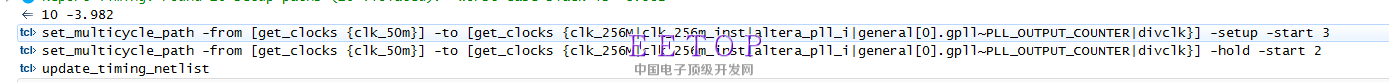

我这样设置后,还是不可以。

set_false_path -from [get_clocks ~] -to [get_clocks ~]

同样试过这样设置,结果还是没有约束成功,是我哪里设置不对吗?

SDC文件正确加到工程里面了吗?

感觉SDC根本没加对

重新设置了一遍,在timerequest Advisor 中 设置好set false path 后再重新编译,为什么还是出现上图中的错误?再看report timing transfer 时,发现之前设置的set false path 已经没有了。SDC 文件正确的情况下

参考以下设置 assignment-->settings-->TimeQuest Timing Analyser-->SDC files to include to the project.

在这里指定你的SDC的路径,希望有帮助 。不要只看结果,先看看过程记录里面是否这个约束生效,有没有告警或者错误,在timing analylis的时候。

之前确实忘了添加SDC约束了。现在没有timerequest 的警告了

没有时序警告了。