求助帖,FPGA,前仿真

时间:10-02

整理:3721RD

点击:

刚刚自学FPGA,做前仿真,结果输入信号都是高阻值(Z),检查位宽也配对,实在找不出问题了,谁能解答我的疑惑,谢谢谢谢

[attach]696590[/attach]

[attach]696590[/attach]

[attach]696590[/attach]

[attach]696590[/attach]

实例化的模块放在initial段后面,再试试

谢谢你呀,不过还是不行呀

- module counter2(clk1k,pinlvkin,rst_n,feedclko,count1kout ); //一秒之内的脉冲数

-

- input clk1k,rst_n,pinlvkin;

- output feedclko;

- output [18:0] count1kout;

-

- reg [15:0] counttest=16'h3e8;//(1000)D

- reg [15:0] count;

- reg [19:0] count1k;

- reg [18:0] count1kout;

- reg [3:0] countnum;

- reg [19:0] feedclknum[7:0];

- assign feedclko=(count[15:0]<=counttest[15:0])? 1'b1:1'b0;

- always @ ( negedge clk1k or negedge rst_n )

- begin

- if( !rst_n )

- begin

- count1kout[18:0]<=16'h000;

- end

- else if (count[15:0]==(counttest[15:0]+16'h010))

- begin

- count1kout[18:0]<=//feedclknum[1][15:0];

- (( feedclknum[0][19:0]+feedclknum[1][19:0]

- +feedclknum[2][19:0]+feedclknum[3][19:0]

- )>>2);//count1kout为1s内的脉冲数作为输出,即为频率

-

- end

- end

-

- always @ ( negedge clk1k or negedge rst_n ) //存储每个单位周期内的脉冲值(T=16ms)

- begin

- if( !rst_n )

- begin

- feedclknum[0][19:0]<=18'h000;

- feedclknum[1][19:0]<=18'h000;

- feedclknum[2][19:0]<=18'h000;

- feedclknum[3][19:0]<=18'h000;

- feedclknum[4][19:0]<=18'h000;

- feedclknum[5][19:0]<=18'h000;

- feedclknum[6][19:0]<=18'h000;

- feedclknum[7][19:0]<=18'h000;

- end

- else

- if (count[15:0]==(counttest[15:0]+16'h010))

- begin

- feedclknum[countnum[3:0]][19:0]<=(count1k[19:0]);

- end

- end

-

- always @ ( posedge clk1k or negedge rst_n ) //产生每个单位时间存储的序号(t=528ms)

- begin

- if( !rst_n )

- begin

- countnum[3:0]<=4'h0;

- end

- else if (count[15:0]>=counttest[15:0])

- begin

- countnum[3:0]<=countnum[3:0]+4'h1;

- if (countnum[3:0]>3)

- countnum[3:0]<=4'h0;

- end

- end

-

- always @ ( posedge clk1k or negedge rst_n )//控制计数周期

- begin

- if( !rst_n )

- begin

- count[15:0]<=16'h00;

- end

- else

- begin

- if (count[15:0]>=(counttest[15:0]+15'h210))//

- begin

- count[15:0]<=16'h00;

- end

- else

- begin

- count[15:0]<=count[15:0]+16'h01;

- end

- end

- end

-

- always @ ( posedge pinlvkin or negedge rst_n ) //在1s内对输入的脉冲进行计数

- begin

- if( !rst_n )

- begin

- count1k[19:0]<=19'h00;

- end

- else

- begin

- if (count[15:0]>=(counttest[15:0]+16'h20))//计数后清零,准备重新计数

- begin

- count1k[19:0]<=19'h00;

- end

- else if (count[15:0]<counttest[15:0])//计数

- begin

- count1k[19:0]<=count1k[19:0]+19'h01;//count1k[19:0]为1s内的脉冲数

- end

- end

- end

-

- endmodule

这是模块代码,你帮我看下,我刚刚自学这个,不是很懂,谢谢您啦

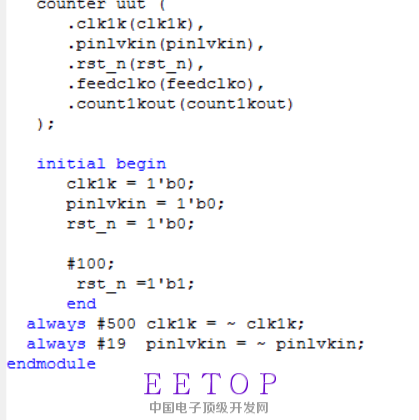

module名是counter2,为什么例化的时候是counter uut?

楼上正解

楼上正解

问题貌似不在这,我把counter uut改成了counter2,依旧没解决,我这样设置激励不觉得有错呀

- module counter_test;

- // Inputs

- reg clk1k;

- reg pinlvkin;

- reg rst_n;

- // Outputs

- wire feedclko;

- wire [18:0] count1kout;

-

- initial begin

- // Initialize Inputs

- clk1k = 1'b0;

- pinlvkin = 1'b0;

- rst_n = 1'b0;

- // Wait 100 ns for global reset to finish

- #100;

- rst_n =1'b1;

- end

- counter (

- .clk1k(clk1k),

- .pinlvkin(pinlvkin),

- .rst_n(rst_n),

- .feedclko(feedclko),

- .count1kout(count1kout)

- );

- always #500 clk1k = ~ clk1k; //产生 1kHz 时钟源

- always #19 pinlvkin = ~ pinlvkin;

- endmodule

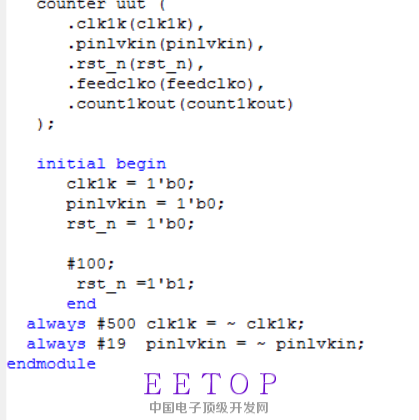

仿真的时候CPU实际上是从前向后顺序执行的,所以module的例化应该放在初始化之后

第二次贴的测试文件里面,实例化怎么写在initial模块里了,而且实例化名字也没有,应该会报错吧,还有你说的是测试信号输出的是高阻态?(是指设计模块的输入是高阻吗?),那很有可能就是你端口没连好了,你可以看看测试模块输出的信号是不是高阻

- module counter_test;

- reg clk1k;

- reg rst_n;

- reg pinlvkin;

-

- wire feedclko;

- wire[18:0] count1kout;

-

- parameter CYCLE = 1000;

- parameter RST_TIME=3;

-

-

- initial begin

- clk1k = 0;

- forever

- #(CYCLE/2)

- clk1k=~clk1k;

- end

- initial begin

- rst_n = 1;

- #2;

- rst_n = 0;

- #(CYCLE* RST_TIME)

- rst_n = 1;

- end

-

- initial begin

- pinlvkin = 0;

- forever

- #20

- pinlvkin = ~pinlvkin;

- end

- counter uut(

- .clk1k(clk1k),

- .rst_n(rst_n),

- .pinlvkin(pinlvkin),

- .feedclko(feedclko),

- .count1kout(count1kout)

- );

- endmodule

这里还是用的counter uut?你确定你的module名字是counter吗?你确定编译没有问题吗?仿真中有没有什么告警和错误?也要仔细看看,那些信息更有帮助。比我们在这里盲人摸象好多了。

嗯嗯,好

timescale 设了吗

设定了,单位是1ps,精度1ns

Unable to copy libPortabilityNOSH.dll to the simulation executable directory:

我检查代码,仿真只出现了这一个警告,是不是问题出在这了?

单位是1ns,精度是1ps吧

怎末可能?1ps=1000ns呀

用什么做软件做仿真?。1 ns =1000 ps

这个我检查了,没弄错,没问题,关键不在这

汗,1ns=1000ps。低级错误呀,兄弟。