请教一个PHY芯片的问题,调试的时候出现的问题

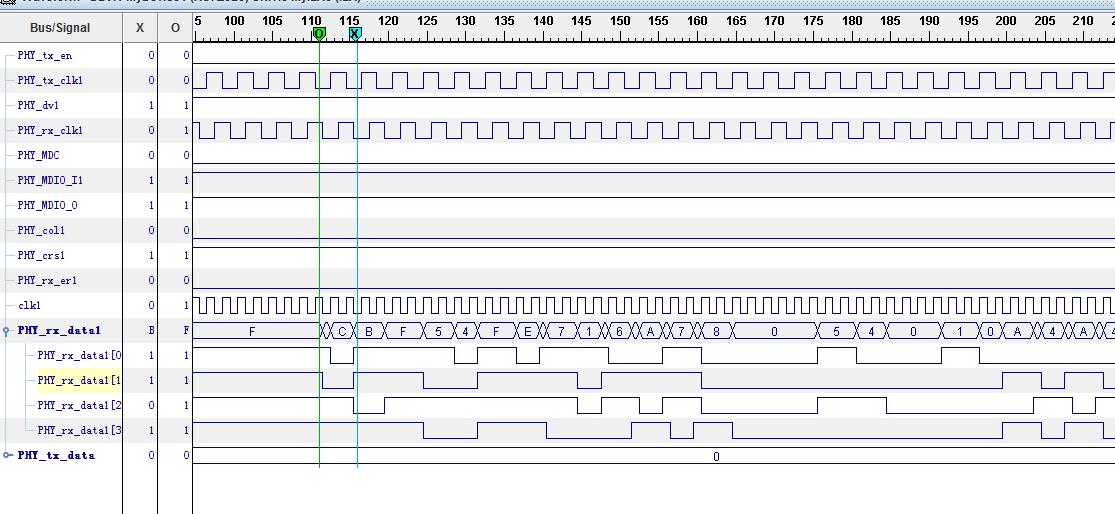

但现在唯一的一个遗留问题就是,在接收数据的时候,接收的时钟(PHY提供)rx_clk 是25Mhz,在该时钟的上升沿或者下降沿rx_data(3:0)为接收的数据,在多数情况下,随着rx_clk 触发沿的降临,rx_data(3:0) 传输半个字节的数据,但是事实上通过chipscope仿真软件的观察,大部分的数据接收都是正确的,也有的时候出现错误:如下图

:

从图中大概可以看到,rx_data1 由F变成C的过程中竟然多了一个过渡的数据,可以看到,这是因为rx_data(0) 没有及时跟着rx_clk 的触发沿翻转导致的,而rx_data(3),rx_data(2),rx_data(1)则及时的翻转。

经过多次的数据观测,这种情况出现的频率并不低,(只要出现这种情况,数据接收必然失真),而且某些情况下,rx_data(3),rx_data(2),rx_data(1) 也会出现翻转不及时。

在ping测试过程中,有些时候测试不成功可能就是因为上面所讲的问题。

这个原因是什么导致的呢?会不会是PHY芯片内部的问题。如果是PHY芯片内部的问题,但很多时候数据的接收都是没问题的。还是焊接的原因呢?最大的疑惑就是这种异常状况并非一直出现,大部分时间是好的?希望大家给我提供一点思路吧,我在这里谢谢了。

额,不看不懂

chipscope的采样时钟是什么

chipscope的采样触发信号是PHY_dv,也就是接收数据为有效的信号,该信号有效的时候,rx_data才有效。chipscope的采样时钟是以太网IP核与ARM之间的AXI总线的时钟信号是100MHz。也就是chipscope的每一个采样的点就是一个总线时钟的上升沿。

总线时钟无法观测,所以引出clk1,这个时钟是总线时钟频率的一半,因此可以判定PHY的发送脉冲核接收脉冲是标准的25Mhz。

你的采样数据是PHY_dv,最好用PHY_dv的时钟去采样该信号。你用的axi总线的时钟,肯定会有采不稳的状况

同意楼上的说法。PHY芯片的RX_CLK和数据都是由PHY芯片产生的,它们之间的逻辑关系应该是由PHY本身来保证的,所以我觉得问题应该不是出在这里。ChipScope的采样时钟应该要和被采样的数据同源,这样采样到的信号才是可正确观测的。

以我多年网络PHY使用经验来看,这个问题是PHY_RXCLK上升沿采样还是下降沿采样的问题。一般的设计,RXD是用PHY_RXCLK驱动(可以参考PHY的说明书),从图中来看,RXD似乎是在PHY_RXCLK下降变化数据,MAC用PHY_RXCLK下降沿工作更好些。

过度数据是因为RXD是PHY_RXCLK驱动,由于内部路径延时不一样,用100MHz的异步始终采样肯定会先后采样到。这个并不是PHY数据错误。

好!

你好,现在网络的调试有了新的眉目。现在有一个问题没有解决。就是假使我用网线将板卡和电脑连接在一起的时候,我对板卡进行了1000次的ping测试。发现ping测试部分成功,而部分没有成功,细细的分析之后发现:网口的绿灯有时候亮,有时候灭。网口的绿灯亮的时候,电脑的本地连接显示已经启用,此刻的ping测试是可以成功的。灭的时候,电脑的本地连接显示电缆已拔出,此时的ping没有成功。电脑这边的网卡是没有问题的,网线也没有问题。于是,我运行了每隔一秒读取一次phy内部寄存器的程序(当然程序运行的时候,网口的绿灯也是时灭时亮,1秒左右更替一下),寄存器的内容也是不断变化的,有时候显示自动协商完成,100M连接已经建立,有时候显示自动协商没有完成,连接没有建立。

phy芯片的ANE引脚(拉高,设置成自动协商模式),还有两个引脚拉高设置成了百兆全双工模式。

请问一下,这个是不是phy芯片不断重启自动协商导致的呀?如果是,应该怎么解决呢?

你的qq号多少?我一直在调试一个以太网的板卡,可能要请教您更多的问题,

请教个问题,rtl8212芯片做LOOPBACK测试时,利用signaltap观察时发现总是会在rxd管脚,一帧数据的最后总为6bf,这是否正常?还有一个问题,RTL8212的网口板子,在FPGA内部做直通测试时,即P1口收到的直接甩给P0口,P0口收到的甩给P1口,同时连接两台电脑,发现交换电脑后,两台电脑ping不通,有碰到这问题的吗

您好,我最近调试板卡也出现了相同的问题。当给电脑和板卡同时上电时,有时二者无法正常通信。而如果将板卡强制设定(不设置为自动协商),则同时上电后,必然可以正常通信。

求教小编

您好,我最近调试板卡也出现了相同的问题。当给电脑和板卡同时上电时,有时二者无法正常通信。而如果将板卡强制设定(不设置为自动协商),则同时上电后,必然可以正常通信。

求教小编

您好,我最近调试板卡也出现了相同的问题。当给电脑和板卡同时上电时,有时二者无法正常通信。而如果将板卡强制设定(不设置为自动协商),则同时上电后,必然可以正常通信。

求教小编

好久之前的我发的一个帖子了。我的问题早就解决了,出现自动协商的原因如下:

控制PHY芯片的所有引脚的电平我给设置成了1.8V。这是不对的。设置成3.3V后,无限制的自动协商的问题消失了。

您好,方便你的QQ告诉我吗?现在有点问题向你请教下。

2132?

您好,请问您一个phy芯片的问题,现在可以用MDIO读写PHY芯片的状态,使用的自动协商模式,网口绿灯可以亮,但就是拿fpga给phy芯片发包,phy芯片通过网口连接电脑,但是电脑上就是无法抓到包,或者我从电脑发包,phy芯片的rxd[3:0]口就一直是没有输出,请问您能指点下吗?

小编有phy的资料么,最近想学习学习

会不会是FPGA控制MDIO时的状态机问题。