慢时钟域采样快时钟域信号

时间:10-02

整理:3721RD

点击:

有两个时钟域 clka :1M,clkb:50M,能实现用1M慢时钟域去采样50M快时钟域的信号吗?

可以呀,让50M产生的信号产生一个大于1us(1M)的电平,然后再用1M时钟去捕获这个电平或者捕获这个大于1us信号的沿。

5555555555555555555555555

常用方法是将快时钟域信号展宽,通过反馈电路将信号再拉低,完成快时钟到慢时钟的转换。

简洁准确,谢谢。

看看,学习学习

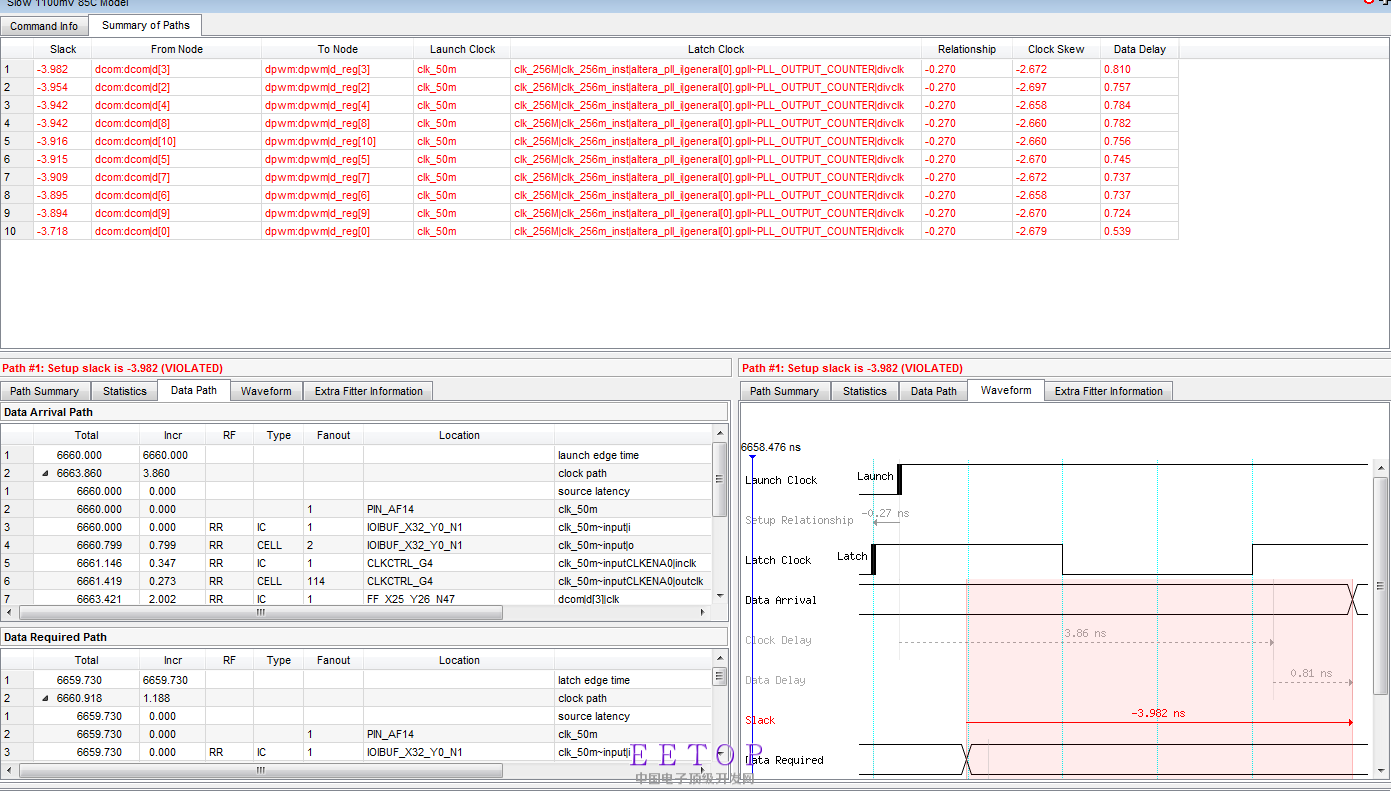

谢谢,学习了。后来查看RTL级发现是 快256m对慢50m时钟采样,然后设置Multicycle Hold 后,为什么不顶用。

clk_50m和后面的那个时钟是同步还是异步?

经过了一个PLL ,慢的时钟是参考时钟,生成的是快时钟,然后快对慢采样

有没有把这两个时钟放到一个clock group里面?我理解这样就是同步的吧。不能当做异步去分析。