pcie扫盲贴

时间:10-02

整理:3721RD

点击:

从速度上来讲PCIE1.0标准 2.5G(8B/10B),

pcie2.0标准 5.0G(8B/10B)

pcie3.0标准8G(128B/130B)

通道来讲:

X1,X2,X4,X8,X16。

中断实现:

1:lengcy INTN

2:传统中断

3:MSI中断。

辅助功能 :

1:功耗管理

2:AER机制。

3:FC流量控制与调节机制。

从结构上来讲分为

GTP+数据链路层+应用层,其中GTP和数据链路层是IP提供的,基本上不需要修改,除非几个特殊的应用

从模式上来讲

rc模式

EP模式

从接口上来讲 :

1IO模式

2:DMA模式,DMA模式分为块DMA(B_DMA) 和 链式DMA(SG_DMA),还有好几个DMA模式,但是没有实际用过。

参考资料:

1:pcie标准教材

2:pcie结构导读

xilinx的DMA例子

1:xapp1052

2:xapp859

3:opencores中的SG_DMA

大家谁还想到了,就继续添加啊

小编先扫这个盲吧:

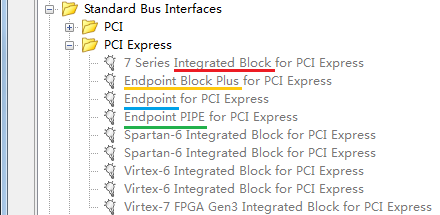

红、橙、蓝、绿,Xilinx的几种IP核有什么不同?那个PIPE的是实现了PIPE的上层还是下层?Endpoint应该不能做RC,那Endpoint Block和Endpoint核又有什么不同?

没有研究过这个,你可以告诉我嘛? 我跟着学习一下,谢谢了

我没做过pcie硬件开发,也没条件用xilinx的开发板。安装ise想仿真一下,一看有这么多IP core,就罢手了。以后有条件、有时间再学吧。谢谢了!

如果自己能搞个sp605就有机会玩了!现在自己如果有时间看看相关知识做储备吧!

简直业良心,新学pcie的看下

新手一个,求交流qq:1098549099

和器件有关。 s6 和 v6 、v5 都有不同 7系列 基本上是相同的

跟着学习一下

进来学习下~顺便混点信元

进来学习下~顺便混点信元

顺便学习一下

谢谢小编~

学习一下

正在被扫盲

pcie首先应该是硬件结构吧

有ALTERA版的吗

谢谢。。

up 好贴,要顶起来

学习了

问下,如果有外部有多个中断信号同时来,采用多个MSI中断向量,该如设计中断上报机制比较合理? 我只会INTA,没玩过MSI

谢谢分享啊

这也叫扫盲?差远了

DMA是针对CPU板卡上的一种访问内存方式,对我FPGA,只有mem read和mem write这种最简单的协议概念,很多新人把DMA想复杂了,但一说其实就是协议里的mem操作,就很容易理解了。

新手,学习了

总结的不错,简单明了。

那你来继续添加哈,

学习了。

谢谢——————

跟着学习一下