verilog非阻塞赋值与always的问题

时间:10-02

整理:3721RD

点击:

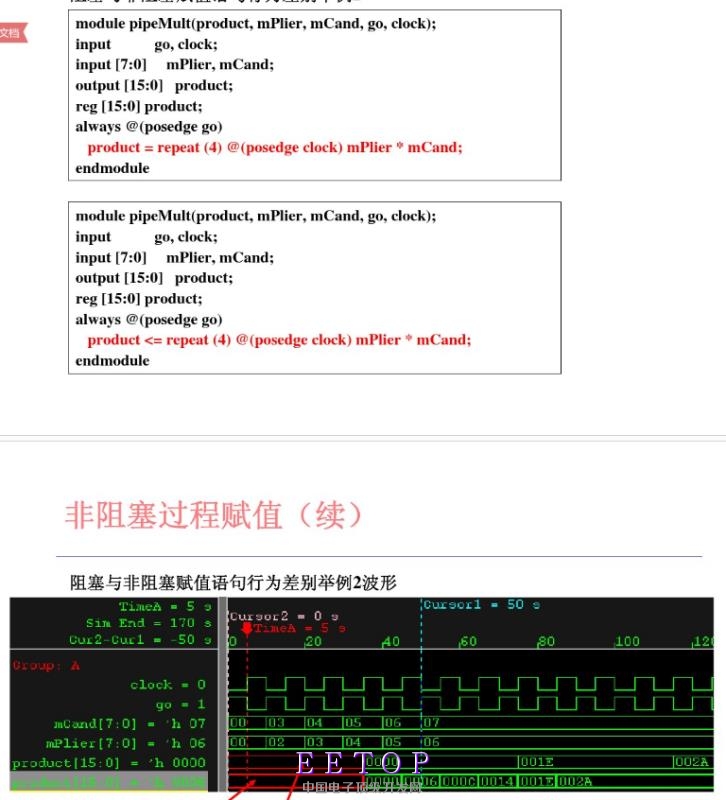

图中的第二段代码的波形为什么这个样子?

我个人理解是在非阻塞赋值的情况下,always被连续触发了,输出的是两个输入端口的乘积,延迟4个时钟后输出。

秀出你的强大了。

不建议这么写进程,尤其是非阻塞赋值,一定要时序逻辑才这么用。你设计的电路一定要符合实际的电路结构,不能任意妄为,VERILOG是描述语言,不是设计语言,一定要遵循规范才行,否则就容易得到不期望的东西。建议最好多看看书上的参考案例,当然一定要很正规的语法书。

谢谢你的建议,我会按照你说的做的。

因为我是转行,这个都是网上教程的代码,一开始对非阻塞赋值没太理解,就来问问~