什么时候用组合逻辑?什么时候用时序逻辑?迷糊中

比如下面例子 :

module add(

input a,b,

input clk ,

output reg [1:0]c1,

output reg [1:0]c2

);

always @(*)

c1 = a +b ;

always @(posedge clk)

c2 <= a +b ;

请问大家C1和C2各有什么优缺点啊? 我只知道C1是从查找表出来的,C2是从查找表-FF出来的。

运算通常可以在一个周期内完成,不需要多个时钟周期

如果综合出来的critical path 比较长,那最好在运算完成后用时钟打一拍,以防止出现meta stable。

个人认为如果你的前后还有其他模块,这个应该就用时序了。加法器的延迟还是挺大的,再跟别的组合逻辑放在一个时钟周期里面就太影响时钟周期了。通俗的说,如果设计比较大肯定要用时序电路的。组合只是描述一个时钟周期内,或者说描述两个寄存器之间的运算用。组合之后必有寄存器给他限制住,等下一个clk来了再让他往下一级寄存器流

那是不是 在设计中 尽量少用组合逻辑呢? 因为我的逻辑中有一个模块(加法器,比较器,选择器)全部是组合逻辑实现的,当时跑到了125M,用时序也跑到了125M,所以我现在就是想不通的

你的意思是 ? 可以详细一点吗?谢谢了。

根据你的timing情况而定。如果没有violation,多用组合逻辑没什么不好的,也许gate还会用的少些。

看情况而定吧,其实时序逻辑和组合逻辑的功能是不同的。时序逻辑就理解为触发器吧,组合逻辑就理解为LUT吧。

是的,时序逻辑就是经过查找表后的两个FF,而组合逻辑是直接经过的查找表, 比如我现在在做一个状态机,是用组合逻辑还是时序逻辑,你可以讲一下吗? 还有各自的优越点?

其实一个ic的输入输出都要有DFF限制住。大的设计中不可能是只用组合逻辑实现的。全用组合是异步电路,并不是同步电路,而我们所说的仿真和模拟都是对同步电路的仿真。你说你跑到了125MHZ,是综合器假设你设计的前后都有DFF, 才能组成一个时序路径,这条时序路径能承受最大125MHz的时钟。否则125M有什么意义呢?至于什么时候组合什么时候时序是按照你的需求定的。假如你的组合电路很大,那么就要等很长时间电路才会得出结果,如果改成时序就可以把它拆成好几级,之间用寄存器隔开,这样就能构成流水结构,算的很快。再比如说好多组 组合电路之间需要配合,需要一起到达一个位置,一起出现一些运算结果,或者是同一个组合电路分给不同的路径用,都需要用时序来控制。如果是真正的设计,一定是时序

ok,谢谢你了,呵呵

状态机的话,稳定性很重要,时序必须保证好,要用时序逻辑,一些逻辑输出肯定是组合逻辑出来的,,到时候看情况你要不要再用触发器打一拍了。

组合逻辑用于算法,时序逻辑满足timing上的要求

有所领悟~

但是我看xilinx的书上 有个三段状态机方法 ,状态机就是采用的组合逻辑,那么这个怎么理解啊?而且有的程序的状态机是采用组合逻辑实现的,有的通过时序逻辑实现的 ,请问小编,比如状态机是采用时序逻辑控制还是组合逻辑控制,这个的依据是什么啊? 是看时序吗? 还是?

?可以讲的详细一些吗? 不太清楚的,

我举个例子啊,

module mux2_1( clk, rst ,a1,a2,c ,out1,out2) ;

input clk ,rst ;

input a1,a2 ,c;

output out1,out2 ;

reg out1 ;

wire out2;

always @(posedge clk or posedge rst)

if (rst)

out1 <= 1'b0 ;

else if (c)

out1 <= a1 ;

else

out1 <= a2 ;

assign out2 = c ? a1 : a2 ;

endmodule

可以讲一下 什么时候用out1 什么时候用OUT2吗?

谢谢了

你好,我现在还有一个疑问啊,

就像你所说的,如果组合逻辑在一个周期内可以实现了,那是不是用组合逻辑可以提高速度呢?

如果频率很高,组合逻辑超出了一个周期的时间,用时序逻辑可以保证下一级的建立和保持时间吧? 而用组合逻辑是不是就会有时序的问题呢?

不知道我的理解正确吗?

是组合逻辑还是时序逻辑主要是看你对于电路需要的理解,写代码时候你应该很明确的知道你写的这段代码用的是组合逻辑还是时序逻辑。我的建议是一般时序逻辑只写成单纯的赋值(一般需有个复位,然后再赋值),不要有任何的逻辑,对应电路上就是一个DFF。而至于前面的逻辑功能采用组合逻辑来进行赋值。

你说的那个状态机我虽然没看过,但我猜应该就是状态的存储是用时序逻辑写的,而状态之间的转换逻辑用的是组合逻辑。不知我理解的对否

是的,是输出信号又打了一拍,这样是不是相当于时序控制了呢? 因为时序控制就是组合控制+FF吧?

状态信号采用时序控制,输出信号也是采用时序存储,那么采用时序存储的优点是什么呢?

可以这么理解吧。专业名词神马的我不太记得住,呵呵

那么为什么状态机的控制输出信号也要采用时序控制呢? 不可以直接控制操作吗? 这是为了时序考虑的吗?

一是可能因为后面逻辑从时序上分析,需要下一拍才用到状态机的输出;二是这样对组合逻辑锁存,可以降低毛刺对后续逻辑的影响;

我是这么理解的,错了的话各位大牛勿喷啊

如果从毛刺角度出发的话,那么是不所大部分的组合逻辑输出最好用时序打一拍呢?

要是单时钟域的同步电路就看你时序需要了吧,因为你只要满足了时序要求的话,就算组合电路中间有glitch,锁存时也应该是个稳定值了。如果你要跨时钟域的时候肯定最好打一拍再送出去同步到另外一个时钟域。

OK,thank you 呵呵,

你好,你的理解是完全错误的。换句话说,你可以认为组合逻辑是实现电路功能的,时序电路中必须包含组合电路,其实就相当于在组合逻辑里面插入了触发器而已,是控制组合的节拍的,通常时序电路中的触发器不做任何运算,唯有时序中的组合能做运算。组合电路无时钟周期,因为根本连时钟都没有。所以你的理解是错误的。

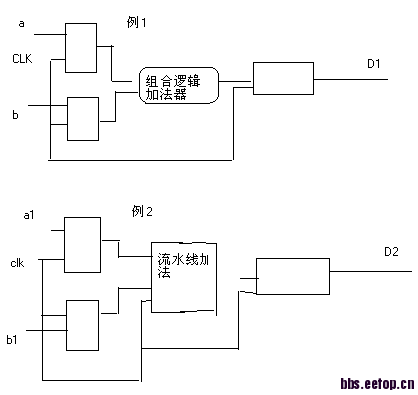

比如图片中的例子,时钟周期为10ns 也就是100M,

输入a,b 都是64位,

在例1中,输入的a,b ,通过组合逻辑加法器来实现a+b , 同时组合逻辑实现的加法器大约占用3ns的时间,

那么在第一个DFF后,直接可以进行加法操作,而不需要等待下一个周期,那么例子一可以完全跑到100M。

而在例2因为采用流水线方式进行操作,那么在第一个DFF以后,要等待下一个周期才能进行加法操作,就占用了一个周期,然后进行流水线操作,而这样导致了程序没有跑到100M,

这个例子的结果我在synplify中验证

过的,

那么这个例子该如何解释呢?

谢谢了,

呵呵

既然第一个组合逻辑加法器能满足时序要求,你干嘛还要使用流水线加法器?这不是自找麻烦么?

第二个例子里面虽然要等下一周期,可是每个周期只需要大约2ns,而且是每2ns都能出来一组结果。也就是说只有第一个周期没有数出来,从第二个周期开始,每个周期出来一个。你只注意到了第一组数~

对的,只有当电路不满足你的时序要求时,你使用了pipeline技术会改善电路的性能,否则没有什么意义