GTX的时钟设置有所不解,求解答。

fpga肯定是用GTX来接受串行的数据,然后转为并行数据。因此只会用到GTX的接收模块。

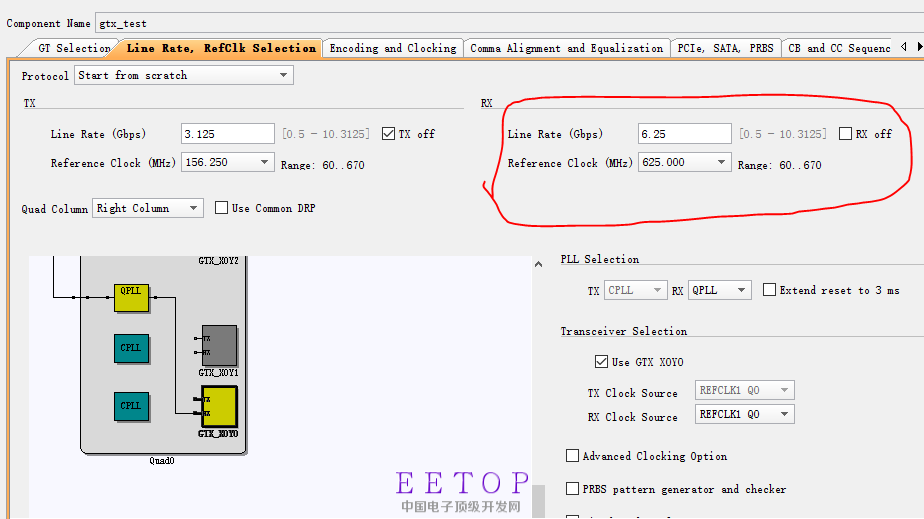

我想最后fpga接收到16bits的并行数据,时钟应该怎么设置,给列位看官设置窗口如下:

不解的就是这个参考时钟的设置。有很多离散的数值可以选择,我不知道它的作用是什么。

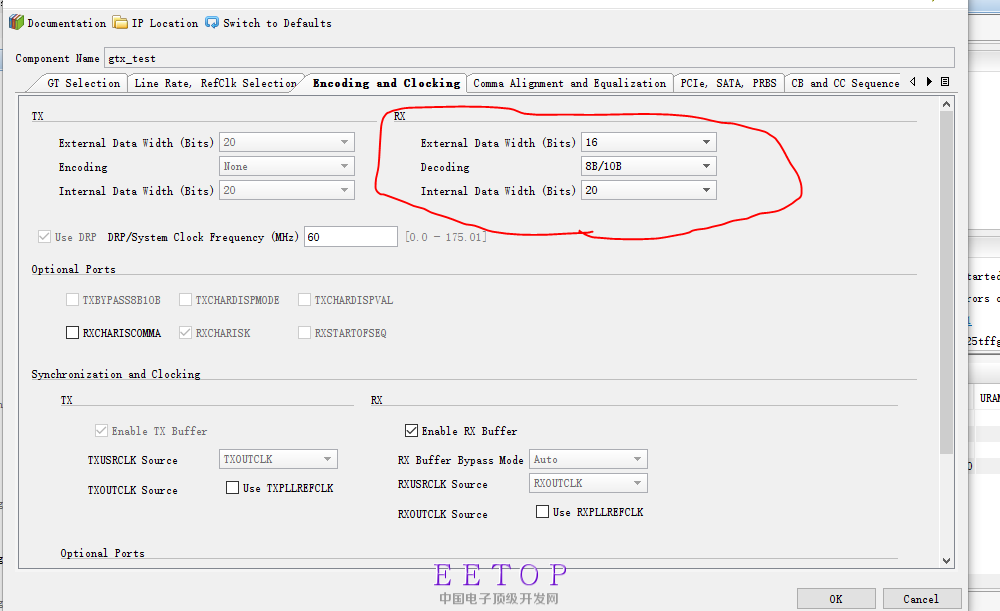

外部数据16位,满足我的要求。内部数据20位,满足8b/10b编码。

我的理解正确吗?

reference clock到底是干什么用的。

你的理解正确

reference clock是用来倍频到3.125G给高速串行数据用的

有这么多离散值说明它们都能倍频到3.125G

谢谢您的回答,我还以为帖子要沉了。

您的说法让我豁然开朗。参考时钟用来倍频到6.25Gbps,要具体根据实际来设置。

这个reference clock是外部输入的时钟吧…PCB上进去的

2楼应该就是正解。谢谢4楼的回答。

一般是倍频到线速率的一半 然后时钟上下沿都带数据 具体可以看看数据手册

你看的好仔细啊。这样的细节都能注意到。我一般都不愿意看几百页的数据手册,就看看怎么用的就行了。

我又有困惑了,串行数据6.25Gbps,我只用GTX的接收模块,由串行的数据变为16位的数据而被FPGA所接收,而且不用编码。那么接收到的16位数据会源源不断进入FPGA,但是16位数据的时钟频率是多少啊?不会算啊。

我算的时钟频率是419,430,400 你们觉得对吗?

我又有困惑了,串行数据6.25Gbps,我只用GTX的接收模块,由串行的数据变为16位的数据而被FPGA所接收,而且不用编码。那么接收到的16位数据会源源不断进入FPGA,但是16位数据的时钟频率是多少啊?不会算啊。

我算的时钟频率是419,430,400 你们觉得对吗?

而参考时钟之中并没有这个数值,那么我在系统中会用到一个参考时钟还有上述算出来的时钟,我隐隐感觉算出来的时钟不对,算法如下:

6.25Gbps=6.25*2^30bits/s;

再除以16就得出我在上述算出的时钟。

列位看官,帮忙看一下啊,,急急急,明天就要给上司讲了。

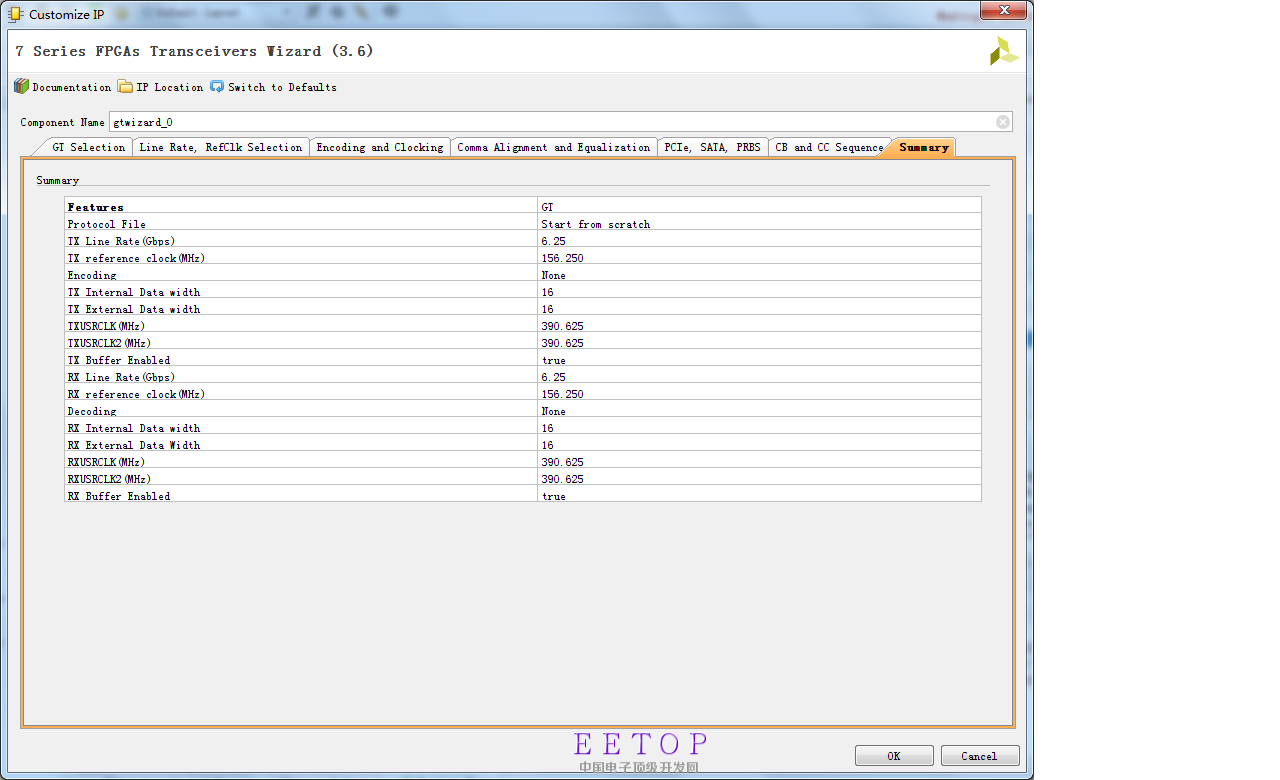

谢谢大家的关心和支持,问题已经解决。是这么算的:

6.25/16*1000=390.625M,这就是用户的时钟频率。

小编,你这个算法应该是不对的吧

6.25G的数据是包括8B/10B编码的,有效载荷6.25x0.8 = 5G

用户侧,并行时钟为:

(5/16)*1000 = (6.25/20)*1000 = 312.5M

个人的理解,仅供参考

这个直接在IP界面设置就能看到

谢谢您的热心回答。390.625M,非常有用,学习确实是需要时间来消化吸收。

您的理解是正确的。我意识到编码是必不可少的,虽然可以设置成没有编码的模式,但是会有严重的后果:数据无法对齐。