FPGA设计中的复位问题

时间:10-02

整理:3721RD

点击:

设计中的全局复位信号来自时序元件(rst_tmp)的输出端(io_rst_bufg_ctrl/rst_tmp_reg/Q), 经过BUFG后输送往各个功能单元模块,并且指定从该引脚出发的所有路径为伪路径,约束语句如下:

set_false_path -from [get_cells -hier -filter {NAME=~ *io_rst_bufg_ctrl/rst_tmp*}]

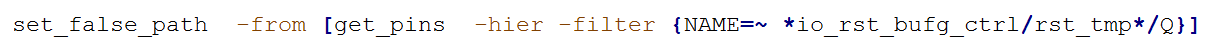

等同于下述约束语句:

set_false_path -from [get_pins -hier -filter {NAME=~ *io_rst_bufg_ctrl/rst_tmp*/Q}]

###<注1:没有指定-to选项,默认指向所有后续时序单元>###

实践中发现,实现后,出现如下现象:

1)查询引脚io_rst_bufg_ctrl/rst_tmp_reg/Q对应的连线(为方便,比如A)

2)查询连线A对应单元,结果只存在io_rst_bufg_ctrl/rst_tmp_reg(不正常,因为没有给出后续BUFG的名字)

3)查询BUFG/I的连线,结果显示不是A,而是B

4)查询连线B对应单元,结果显示有两个:BUFG、io_rst_bufg_ctrl/rst_tmp_reg_replicate(寄存器复制)

5)查询io_rst_bufg_ctrl/rst_tmp_reg_replicate/D对应连线,比如:C

6)查询连线C对应单元,结果包括:io_rst_bufg_ctrl/rst_tmp_reg、io_rst_bufg_ctrl/rst_tmp_reg_replicate

###<注2:即使在约束语句中增加-include_replicated选项,扔改变不了上述情况的存在>###

###<注3:在实现之后,再次运行上述set_false_path命令,可以消除这里所述的负时序路径>###

整合上述信息,发现发生了寄存器复制,原寄存器输出连线丢失后续单元,并且从复制寄存器输出管脚开始的路径,仍存在路径不满足建立保持时间。

疑问:

1)寄存器复制,发生在布局布线阶段,旨在缓解由于较大扇出带来的时序问题。那么,在已经指定BUFG增强后续驱动能力的前提下,这里为何要复制寄存器呢?

2)原寄存器的输出管脚的连线为何没有与后续BUFG/I连接起来?(似乎是被复制寄存器的输出管脚与BUFG/I之间的连线替换掉了)

3)约束语句也适用于复制寄存器(字符串匹配的到),那么为何从复制寄存器出发的路径,仍存在负时序路径呢?

4)设计中人工施加BUFG是否能够强制指定全局时钟网络对复位信号进行布局布线?

外话:

VIVADO综合器在各个阶段(综合-->优化-->布局-->布线)都以前一阶段的结果为基础,同一个XDC文件会被综合器分析几次?

希望相关朋友各抒己见,帮忙解惑,谢谢

竟然没有人回答我的问题

没有弄过vivado,帮你顶上去

谢谢!发了这么多天,竟没有一人提些许看法,哈哈哈。

谢谢!发了这么多天,竟没有一人提些许看法,哈哈哈。