FPGA中FIR IP核的初始延时问题

时间:10-02

整理:3721RD

点击:

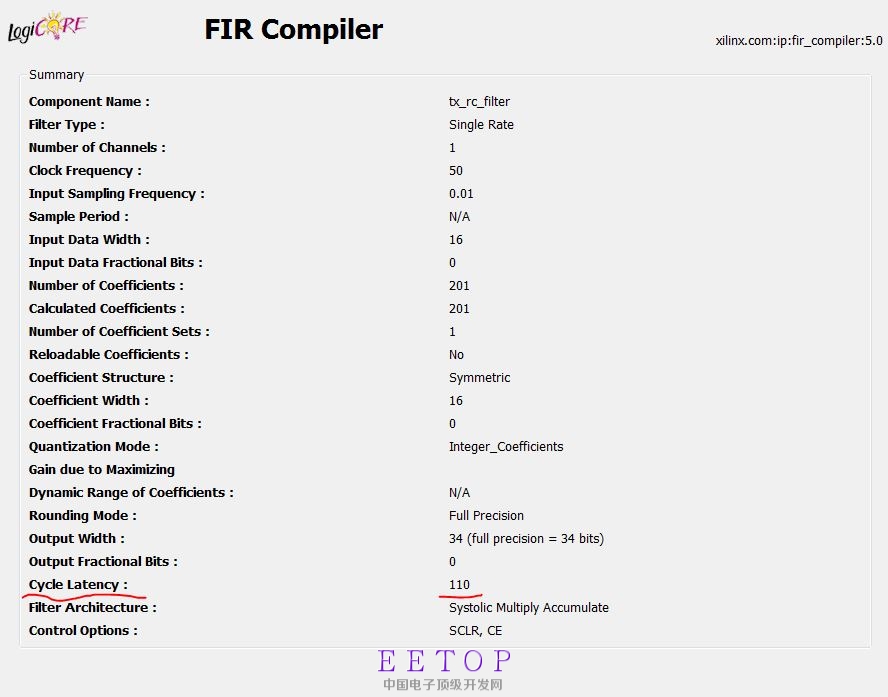

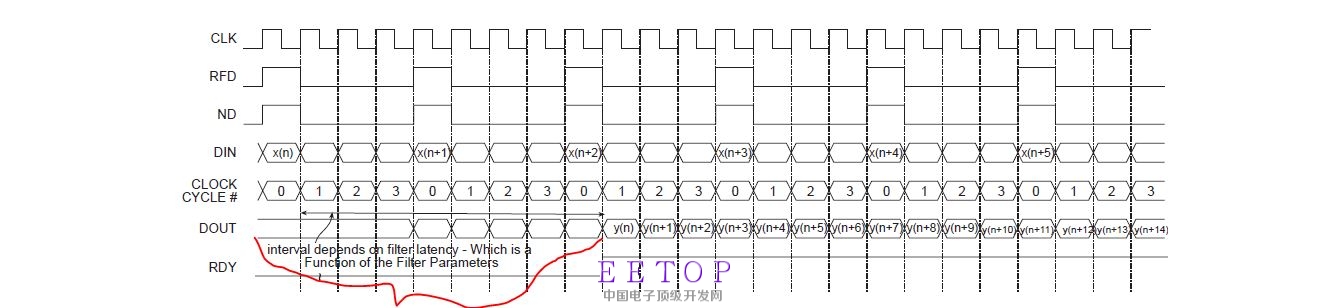

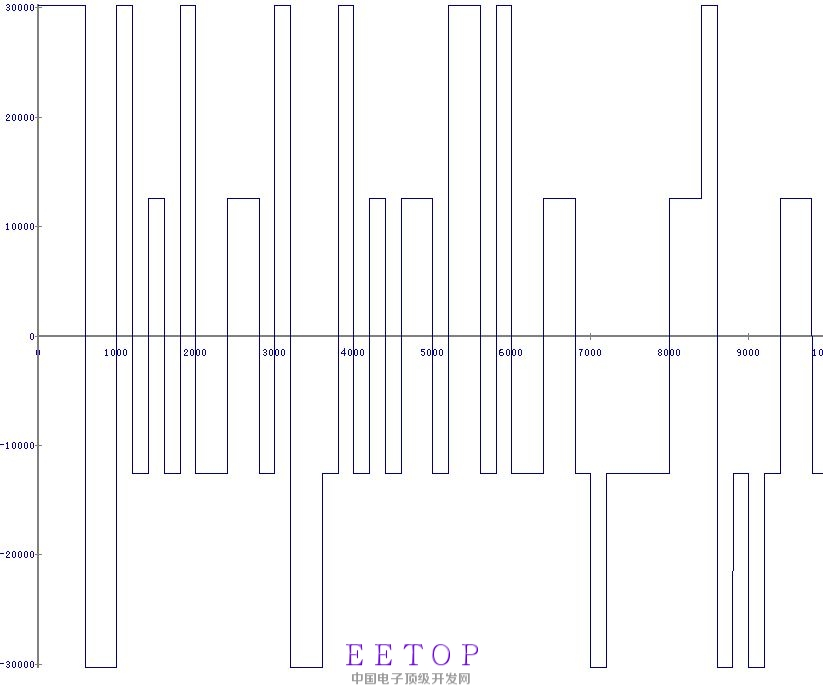

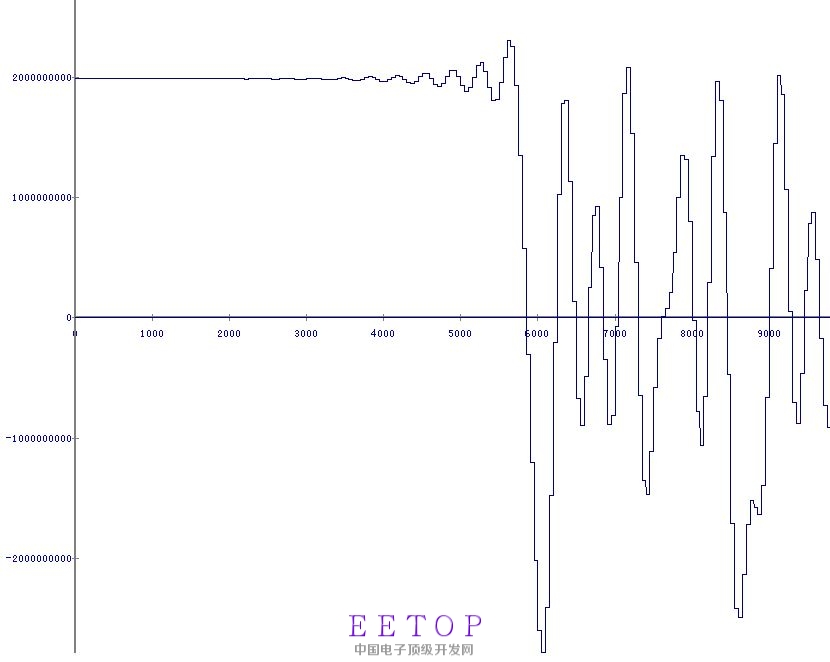

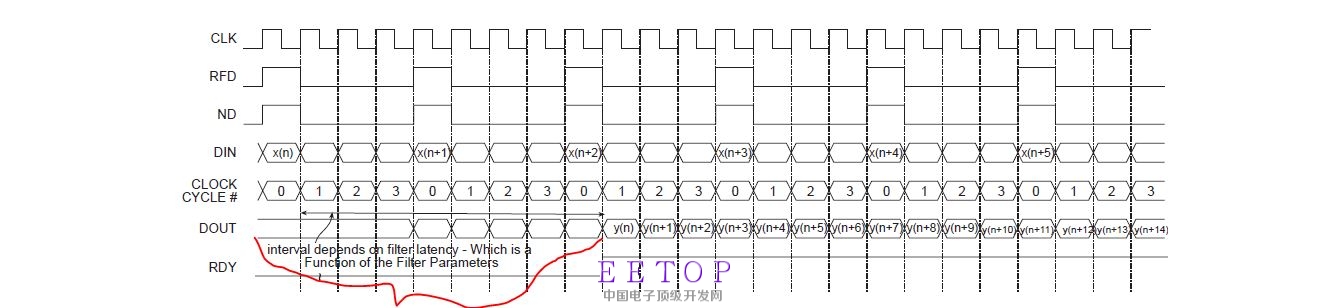

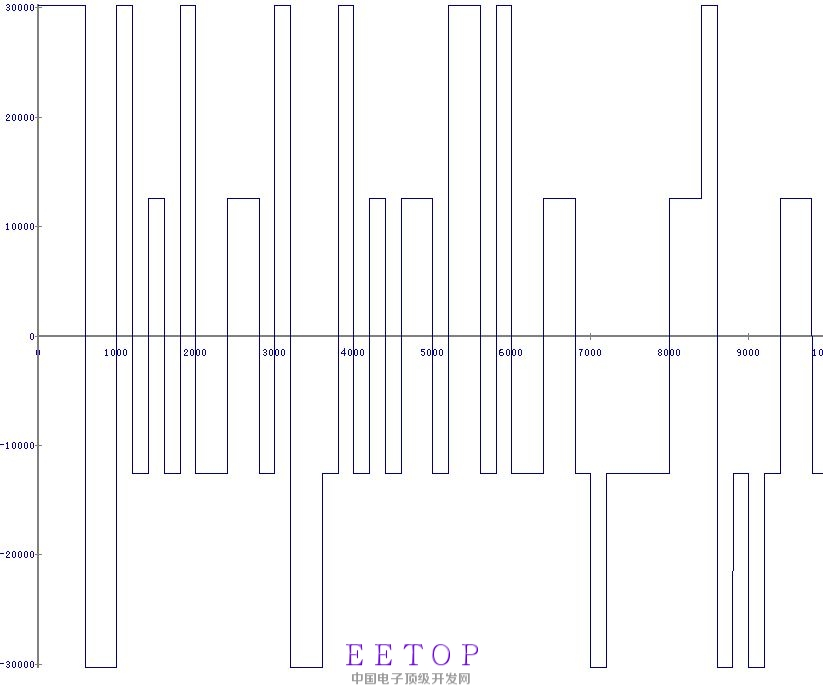

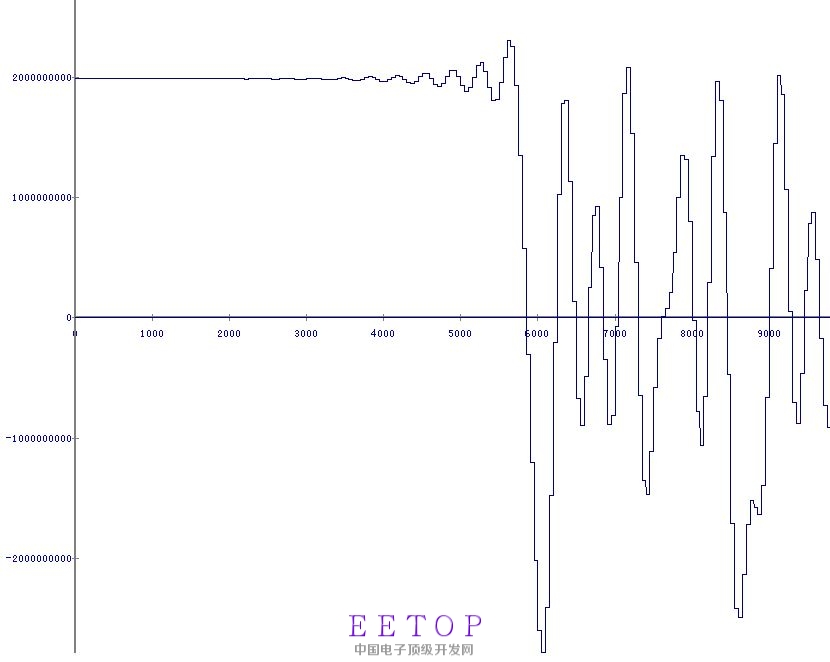

最近在做滤波器,首先用MATLAB的FDATool生成了滤波器系数,201阶。然后在FPGA工程中调用FIR IP核,把系数文件导进去,输入进FIR IP核的数据速率为2.5k,采样速率为10k,FIR工作时钟为50M。接着用Chipscope抓取数据时发现第一个送进滤波器的数据会延时10ms输出,不明白这个延时是怎么产生的。难道是滤波器将10k采样数据存在一个201阶的移位寄存器中后与抽头系数做乘累加,只有当201阶的寄存器都采样到数据后才会输出第一个数据?第一张图是输入滤波器数据,第二张图是滤波器输出数据

FIR的群时延,对称的FIR滤波器来说,是阶数的一半。

滤波器个抽头的初始值为0,所有前面有一段计算稳定的过程。

谢谢,昨天看了一下自己生成的IP核最后的Summary,发现确实是有clock latency 是11ms正好符合Chipscope上的现象。