vivado mig (DDR3)仿真问题求助!

我后来改用micron的仿真模型(生成ip时器件选择是micron的),结果一样。一时不知道如何解决!望不吝赐教

我是一直往DDR仿真模型里写,但写的数据量很小,然后,模型提示读了,可是我是只写不读的呀!我对ddr仿真模型还不很很懂,先谢谢大家

难道仿真模型对写入的数据个数有限制?必须先写后读?怎么修改参数?现在一头雾水!不知如何下手了,望前辈指点迷津,给个思路也好!谢谢

前排占位支持了,嘿嘿

LZ最后解决问题了没有?

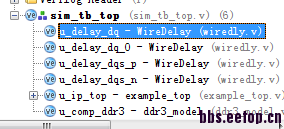

LZ在么,可以看下你仿真例程出来的波形吗?你用自己的项目工程外加ddr3_model.v(xilinx生成ip时生成的)仿真时,是只加了ddr3_model一个模块还是

小编解决没?

我也是遇到类似问题:用xilinx生成的mig core 和模型仿真,直接初始化的model中的memory,但是读数据时memory_used的信号一直异常,导致模型出来的数据是x态;请问大家在初始化memory时是怎么弄的,谢谢!

同问呀,谁解决了回答一下呢

我的init_calib_complete一直为低,有没有人知道原因呢?

仿真得需要110us - 120us左右,那个信号才会拉高的,时间不够。

小编 ddr3的读写过程 搞定了没有 MIG7用户接口中 app_*这几个信号的逻辑怎么用呢

请问小编,问题解决了么? 本人也遇到同样的问题,仿真中,在连续写入一些数据之后,app_wdf_rdy一直拉低,显示DDR3的状态INFO:READ ,但是我的cmd给的是3‘b000. 感谢小编,

我开始也遇到了类似的问题,后来发现原因是app_wdf_end信号没用对。

这个信号是指示最后一个数据用的。也就是说应该只在最后一个数据写入时置高。而我当时没有认真看,把它和en信号同时置高了,DDR一看,心说数据早就完了么,还给什么rdy信号呀。

也许和这个问题是同一个原因。

init_calib_complete仿真到100-120us就变为高电平啦~