verilog的系统任务怎么仿真?

首先,你得多看quartus的帮助文件,得弄清楚这个工具的功能。

2,你得弄清楚开发FPGA的流程。

quartus是针对altera的fpga的综合布局布线的工具。是不能做仿真用。

他能支持的verilog语句,只能是可综合的verilog的语句,这个是verilog中的一个子集。

做verilog的仿真,目前主要是有3大仿真工具,分别来自3个大的EDA公司: synopsys的VCS, cadence的IUS(ncverilog)和mentor 的modelsim。这些系统任务都是不可综合的。这个论坛里的这些工具都下到,破解也都有。

大公司里做simulation的synopsys的vcs和cadence的IUS的应用是比较多的。

quartus II 不支持这种系统任务和函数。如果是windows系统就用modelsim仿真吧,也是FPGA的最好的搭档。安装好modelsim后,在quartusII里可以设置关联,自动调用modelsim,很方便的

还有我想请问下用modelsim可以产生文本文件么?比如像$display这样的语句,我想观察它显示的值的数据,我用了modelsim都是看波形的,不知道有没有这个功能

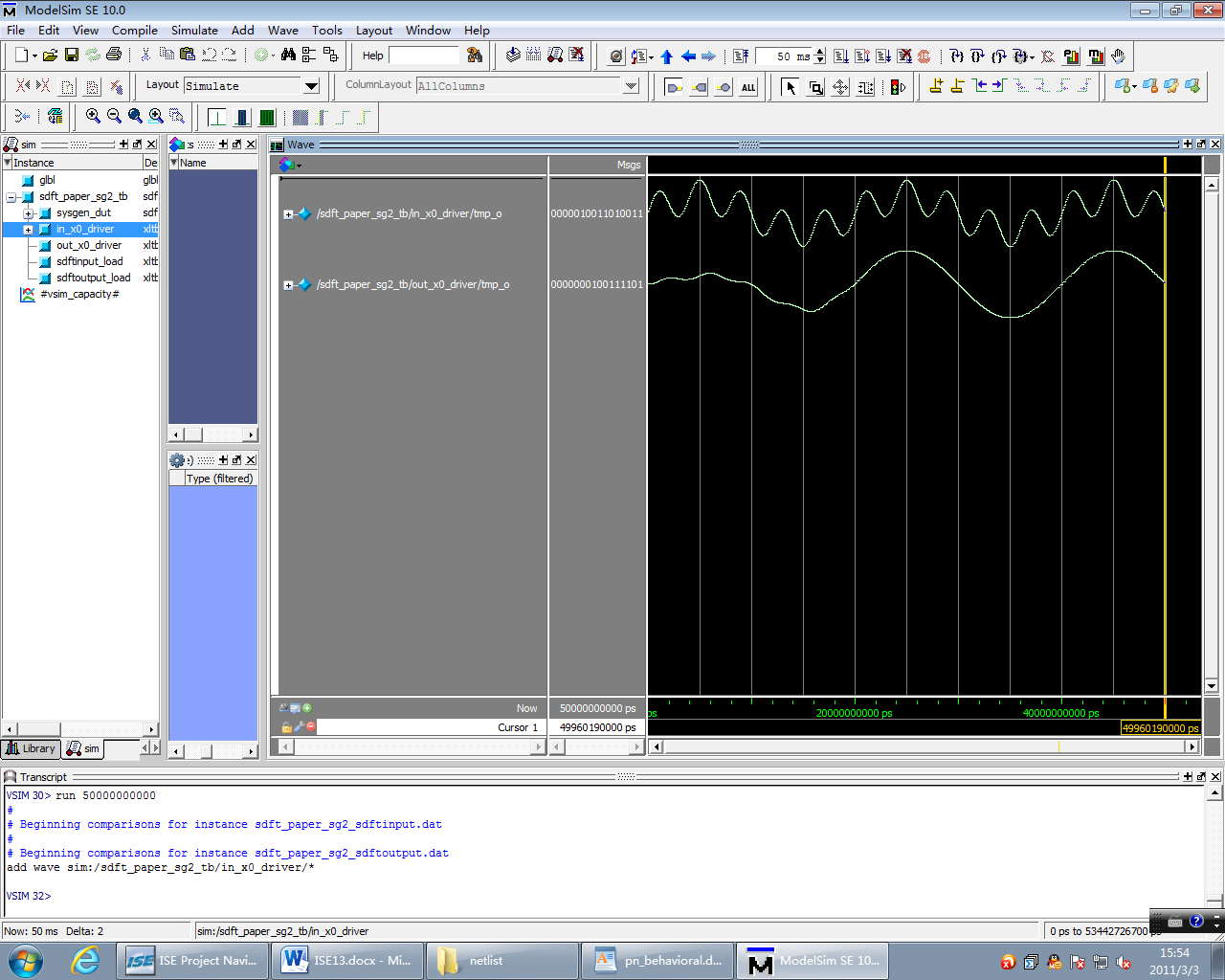

有文本的,在modelsim的窗口下方有个叫transcript,里面就是仿真的记录,$display的结果都在这个transcript窗口里。网上找一个图片:

如果要自己单独保存一个文本也可以用$fopen, $fdisplay, $fclose,这边有个例子:

http://hi.baidu.com/tanglj86/item/f60874c3c885c41a0bd93a66

希望用帮助

非常感谢

新手首先要弄懂什么叫可综合不可综合,什么叫阻塞

好多大神,收货很多啊