如何让begin ... end 内的程序严格顺序执行呢

时间:10-02

整理:3721RD

点击:

个问题,如何让begin ... end里面的程序语严格顺序执行呢,因为我发现我的程序里面它会偶尔不是按照我的意思执行,比如说,我下面的程序语句

else if ((pulse_peak > 602) && (pulse_peak <= 2048))

begin

number_46_50 <= number_46_50 + 1; //record the number of channel 20

total_number <= total_number + 1;

transit_time <= 0; //reset the transit_time equals zero,

end

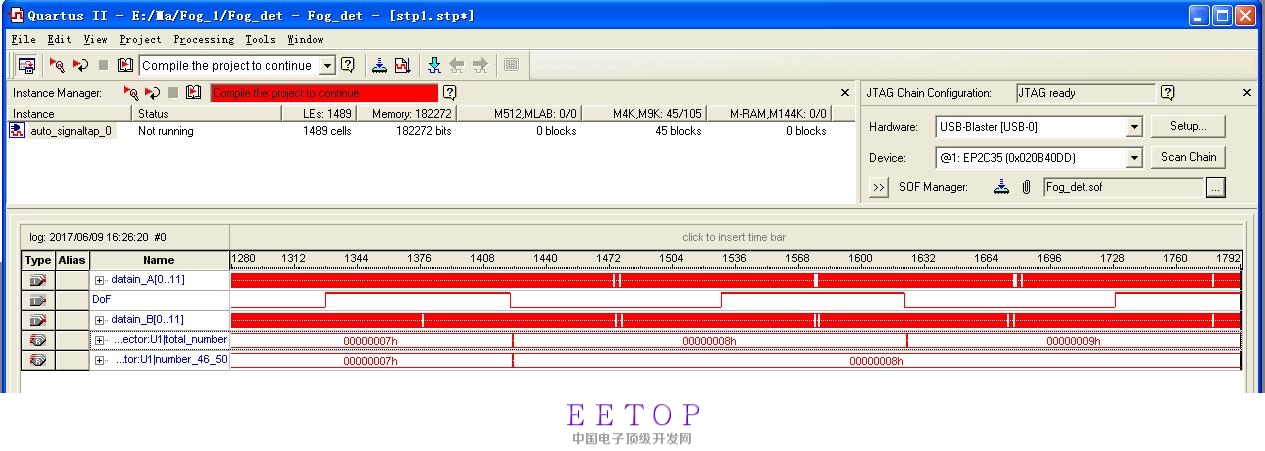

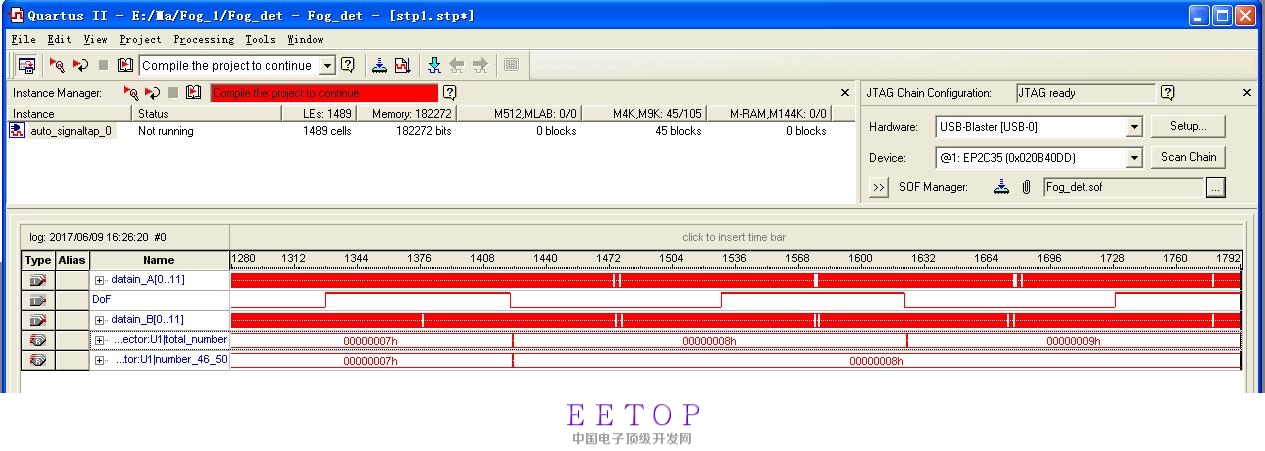

我的原意是当符合else if 内的条件时, number_46_50 自动加1,然后总数total_number 也加1,可是我最后的结果却是total_number 都会严格加1,可是number_46_50 有时就不动,还保留原值。具体可以看图件Signal Tap所抓的实时波形,total_number 由08H增加到09H,可是number_46_50仍保持08H,为什么呢?有没什么方法可以克服?

谢谢各位路过的先!

else if ((pulse_peak > 602) && (pulse_peak <= 2048))

begin

number_46_50 <= number_46_50 + 1; //record the number of channel 20

total_number <= total_number + 1;

transit_time <= 0; //reset the transit_time equals zero,

end

我的原意是当符合else if 内的条件时, number_46_50 自动加1,然后总数total_number 也加1,可是我最后的结果却是total_number 都会严格加1,可是number_46_50 有时就不动,还保留原值。具体可以看图件Signal Tap所抓的实时波形,total_number 由08H增加到09H,可是number_46_50仍保持08H,为什么呢?有没什么方法可以克服?

谢谢各位路过的先!

看看你这个变量是不是还有其他地方赋值?

大哥,你需要学习基本的数字设计的知识。这不是写C, C++程序。

把程序贴全