在FPGA设计的时候添加门控时钟总是会有hold time违例

always @ (en_start or clk)

begin

if (~clk)

ENC = en_start;

end

assign clk_gated = ENC&clk;

请问各位一般做门控时钟的时候怎么做呢?

一般都是做ASIC的时候再dc中用工具自动插入门控时钟的,像你上面这种搭电路的方法不可靠,

插入门控代码一般这样写:

always@(posedge clk or negedge rst_n)

begin

if(!rst_n) D_out <= 1'b0;

else if(EN) D_out <= D_in;

end

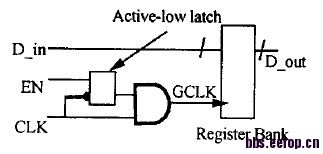

在dc中设置一些命令就可以插入你图上所示的门控时钟结构了,FPGA中DFF资源比较多,一般都不建议用latch了,如果fpga中也能有上图的单元结构的话,倒是可以用的,fpga中如果处理门控,还请高人帮助了哦

你的时钟路径延时比数据大,自然会有问题。

FPGA中不要自己手工写门控时钟,有专门的例化可以调用,而且,尽量用使能。

你这样写门控时钟,时序分析都没法弄。

在FPGA中最好不用门控时钟,可以尝试改成使能控制,使得整个设计都是同一个时钟下的同步设计,如下:

always @ (en_start or clk)

begin

if (~clk)

ENC = en_start;

end

always @(posedge clk or negedge reset_n) begin

if(~reset_n)

else if(ENC)

end

设计中必须要门控又怎么处理,求答案

去xilinx官方论坛问问

如果依照上述的圖來寫RTL Code的話,如下所示:

// RTL Code

module gate_clk_dff(

input

[1:0]

D_in,

output

reg [1:0]

D_out,

input

CLK,

input

EN);

reg

en_lat;

always@(CLK)

begin

if(~CLK)

en_lat <= #1 EN;

else

en_lat <= #1 en_lat;

end

assign GCLK = CLK && en_lat;

always@(posedge GCLK)

begin

D_out <= #1 D_in;

end

endmodule

// TestBench

module tb_gate_clk_dff();

reg

[1:0]

D_in;

reg

EN;

reg

CLK;

wire

[1:0] D_out;

always

begin

#10 CLK <= 1'b1;

#10 CLK <= 1'b0;

end

gate_clk_dff gate_clk_dff(

.D_in (D_in),

.D_out(D_out),

.CLK

(CLK),

.EN

(EN)

);

initial

begin

CLK = 1'b0;

EN = 1'b0;

D_in = 2'b10;

repeat(2) @(posedge CLK);

@(negedge CLK);

EN = 1'b1;

repeat(3) @(posedge CLK);

$stop;

end

endmodule

至於會有hold time的問題應該是你用Gate Clock,所以軟體在算Timing 的時候會比較不好算.