用fpga实现驱动sja1000遇到的问题

时间:10-02

整理:3721RD

点击:

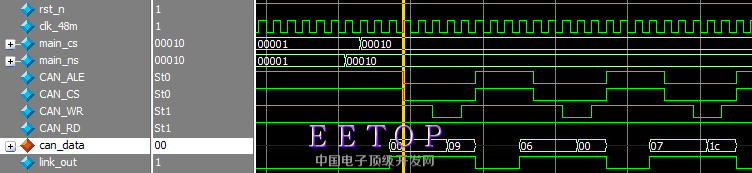

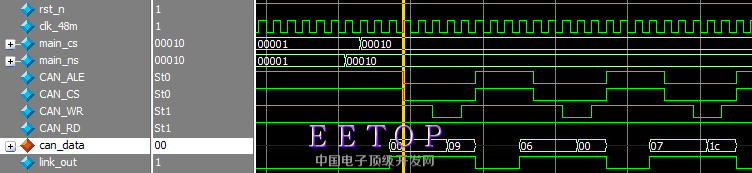

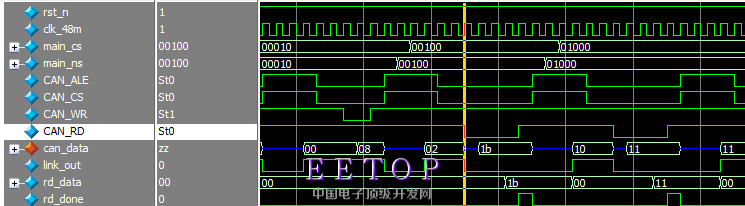

各位好,我现在用fpga驱动sja1000实现can通信,但是程序下载到板子后,有的版本可以正常通信,修改一点之后就不能实现通信了。请问是因为底层驱动的时序有问题还是因为时序不可以?但是时序报告我也查过了,timing时钟余量不满足的和can通信是没关系的。请问是什么原因呢?附图为功能仿真的读写时序图。工作时钟是48M。