FIFO 最后一个数据读不出来? 已解决!

时间:10-02

整理:3721RD

点击:

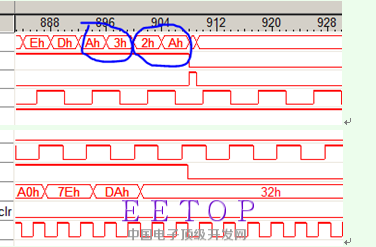

前段时间调试,FIFO最后一个数据读不出来,在下一次读取的时候作为第一个数据读取出来了。

在EETOP,有人遇到了同样的问题。

具体的硬件连接如下

数据 -》 FPGA内部FIFO -》 FPGA内部时钟进行读取。

时钟

其中,数据是88E1111芯片的数据,通过txclk 发送给FPGA,FPGA经过一个FIFO进行同步,将外面的时钟源的数据同步到本地来。

具体现象如下:

(图片怎么传?)

数据本来是DE A3 2A 结果最后一个数据2 读不出来,成了DA 32 (请忽略我做了高地位转换)

是不是很明显?

问题发现:

将PHY的时钟进行时钟约束,发现做不过去。

问题解决:

将PHY的时钟通过全局时钟引脚引入,然后再送给FIFO。

解决办法:

1.最好是芯片的时钟通过全局时钟引入fifo_wrclk/rdclk,

2.对时钟进行约束,看是否可以通过!不通过很可能会出问题!

3.电源一定要稳定,越稳定越好!

4. 地线一定要接好!可以通说明数据通道没问题,偶尔丢包说明不稳定!

5. FIFO本身不需要做任何改动,正常情况下,同步阶数选择3-sync 或者2-sync并没有区别,show ahead mode 和 normal mode 有很大区别,一般默认normal mode就够了,不要改!

--------------------------------------------------------------------------------------------------------------------------------------

附带小编血泪史

6.接口电气特征。当初设置FPGA弱上拉,设置unused pin: set as input tri-state & weak pull up,ARM开漏输出output_OD,结果电流一直从FPGA向ARM灌,FPGA周期性死机。

将FPGA改为set as input tri-state ,不用弱上拉,电气恢复正常!

希望对大家有用!

楠竹

20170515

😬