modelsim时序仿真该如何看

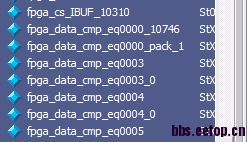

在做时序仿真时,发现很多信号名都变了,无法和我原文件名对应了,我原来文件名是fpga_cs,fpga_data(16'h0000),该如何恢复成我原来信号名?我觉得功能仿真和时序仿真差别挺大的。

请高手赐教~

看看你添加的对不对啊

你设计中的信号在综合的时候都是要和具体的元件管脚相对应的,所以一般你定义的一个信号路径,可能会被打散到很多个元件组合中去,不过它会保留相关的名字,只不过加上很多后缀,具体路径可以打开网表搜索,时序仿真确实是比较麻烦的,因为把结构都打平了,需要一定耐心。

个人感觉时序仿真不应该用modelsim去扣 而是用时序分析加约束看会比较好

谢谢各位答疑,拜谢~

现在也觉得时序仿真不是很方便,因为信号都被打散到很多个元件组合中去了,根本不方便观看,,时序仿真成功的那瞬间幸福完全没有了~···

打算学习静态时序分析(STA),希望不难,,不知道有没有好的资料推荐?

如果觉得时序仿真很麻烦,需要“看”,那只能说明你的testbench写的太差了。

通常,一个prj,在rtl coding阶段同步的进行编写testbench,testbench跟rtl

code一样需要一定的coding style,其中之一就是不要眼睛看波形。而是通过testbench

发送激励,接收dut回发的信号,并自动判断对错。这样子,只要你的dut顶层port名字不变,

那么前后仿真的整体环境应该是一致的,基本不用修改。

时序仿真的意义,就在于尽量去弥补sta无法cover的时序部分,主要是timing exception的path,

这也叫做动态后仿真。后仿真如果有timing violation时,才是真正需要去观察分析波形的时候。

sta是个很大,很深的题目,慢慢研究吧。很多公司的pt工程师,都未能真正掌握sta。你需要从

最基本的数字电路开始学习,path的timing分析等等,网上资料和书籍很多,像google book也可以

去搜索一下。

ls的正解。时序仿真的时候,不用你原来的RTL代码了。综合后和布局布线后的名字和你原来的名字肯定是不一样的

要是你用的是quartus的话在setting->simulation->more eda netlist writer settings选择maintain hierarchy选on,这样的话你的网表里可以保持你的命名,但不是所有的都可以,有的你自己的命名可网线可能会被优化掉,所以要看你的代码风格了,时序问题最好还是STA了,这种仿真想做到100%的覆盖率是很困难的。

quartus也可以仿真

学习了~

您好,如何像你说的那种不用看波形,dut自动判断结果,小弟新人一枚,求指导?