请教个时序约束的问题

时间:10-02

整理:3721RD

点击:

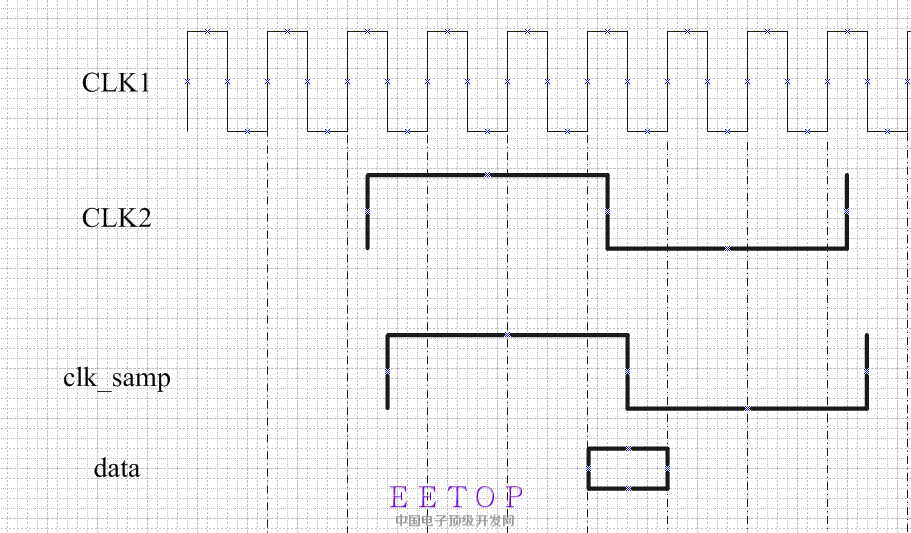

外部输入有字时钟clk1(240MHZ),帧时钟clk2(40MHZ)和数据先用clk1的下降沿对clk2进行采集得到clk_samp,同时用clk1的上升沿对数据采集得到data,如下图所示

再用clk_samp的下降沿对data进行采集,这就是说clk_samp的下降沿与data到达寄存器的时间差必须在2ns之内

这个时序约束该怎么写?

你这个问题里是不是少了一个很重要的条件?数据data的速率是多少?看你的描述像是40M?是同步的吗?如果确是同步的,随路时钟是哪个?

不过话说回来,240MHz的外部时钟可不低,尤其双沿都还要采样。这样的时序分析模型,约束很难达到目的。RGMII接口125MHz双沿的速率对板内PCB布线和时序约束的要求就比较高了。

另外行波时钟clk_samp对于时序约束也是挑战。

建议仔细分析一下整个系统,找出更合理的处理方法。就从你描述的情况来看,这个东西很难办。

数据速率480Mbps,经LVDS后生成data,再由clk_samp采样!

用 create_clock - waveform {rise, fall } ... 去约束。

btw, clk的约束仅仅是“描述”, 即让synthesis或STA 工具知道你想要的clk pattern。CTS得后端搞定并propagate。