各位大神,在写FPGA程序的时候遇到一个很诡异的问题

时间:10-02

整理:3721RD

点击:

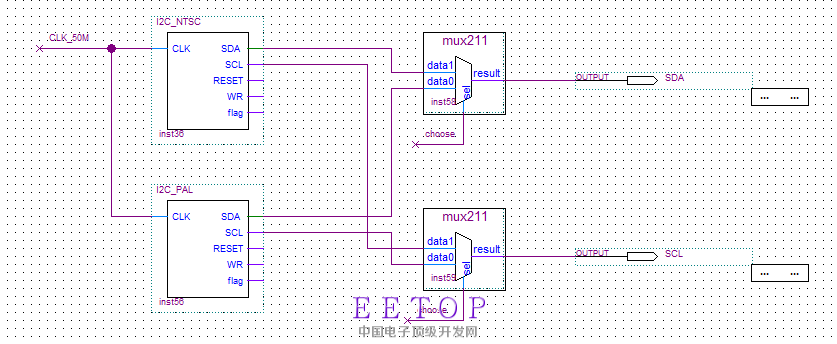

在FPGA内部模拟了I2C总线模块对视频编码芯片进行初始化,当在工程中只放I2C_NTSC或者I2C_PAL任意一个时,对编码芯片的初始化都能成功,但是如果将两者如图放置,再用选择器进行选择时,初始化就会出问题。上面两个模块除了初始化的数据有所不同,其它地方都一致。像这样的话两者之间也会有影响?

SCL信号跟SDA信号走的不是一个选择器,延迟是否一致?用一个选择器,同时选择这两个信号不就行了

虽然不知道你的I2C模块是怎样实现的,但你放2个再通过mux,肯定不行啊。

因为I2C的2条数据线是双向并且开路输出,你用单向的mux怎么能行?

要实现2 个I2C接口的选择,有两种方法:一是片外加模拟开关,二是分别切换SCL/SDA的控制通路及数据通路,例如输出允许oe,数据输出及数据输入,每个PIN(SCL、SDA)需要3个mux,2个pin需要6个mux21。

为什么每个pin需要3个mux?这一点不是特别明白。

双向PAD需要至少3条线,一条输出控制脚OE,一条数据输出,一条数据输入。