请教源同步输出约束问题

请问各位朋友源同步输出数据在为什么能在时钟有效沿的附近变化?为什么会和原先建立时间和保持时间的规定相反

这说的是输出端口处时钟和数据间的关系,任何情况都是正常的。并不是一个寄存器的时钟和数据的关系。

时钟沿前2ns到后1ns是数据无效窗(数据不确定区)。

应该理解成,外部器件的时序要求。例如 DAC 的接口时序。FPGA输出的时钟和数据满足这个时序就OK。

再请教下您

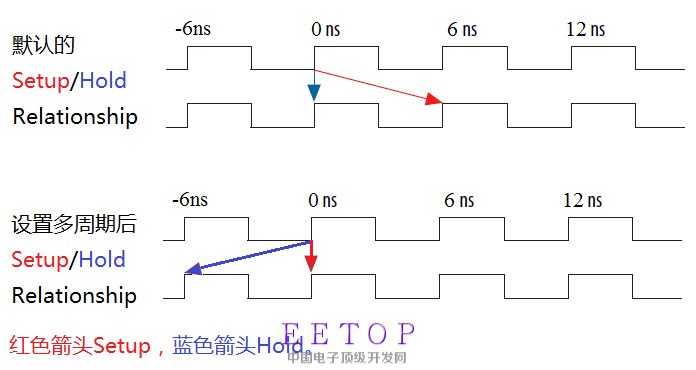

接收方一般是用源同步提供的随路时钟CLK_STROBE对数据DATAQ进行采样,那么图中对DATAQ变化窗口的约束对后续的采样的影响是什么?下面是对DATAQ变化窗口的约束:set_multicycle_path 0 -setup -to [get_ports DATAQ]

set_multicycle_path -1 -hold -to [get_ports DATAQ]

set_output_delay -max -1.0 -clock CLK_STROBE \

[get_ports DATAQ]

set_output_delay -min +2.0 -clock CLK_STROBE \

[get_ports DATAQ]

你的约束把 setup 和 hold relationship 都设为0。因此,设置的值 max = -1,min = +2,就不好理解。

参照 Altera 的文档 AN433,约束如下:

set_multicycle_path 0 -setup -to [get_ports DATAQ]

set_output_delay -max -1.0 -clock CLK_STROBE [get_ports DATAQ]

set_output_delay -min -4.0 -clock CLK_STROBE [get_ports DATAQ]

# 最小延时是 -6+2 == -4

其实,这与你的约束是等效的。

负的延时可以理解成,在外部器件里面,时钟比数据延时更长。这样时钟就可以捕获到同沿数据了。

真是麻烦您了,但是这个约束是为了保证DATAQ与CLK_STORBE在输出端口满足变化窗口的关系吗,这有什么用呢?还望请教下。

FPGA满足外设的时序要求就OK。至于外设怎么锁存数据是外设的事情。

并不是约束正确就可以满足时序要求,软件只能说尽力满足,如果时序不满足,例如setup,hold余量不足,就要在设计中作些调整。例如,增加输出时钟路径延时等等。