Quaruts II门级仿真的时候出现 Hold不满足

时间:10-02

整理:3721RD

点击:

always@(posedge RSTN or posedge Rx_data)

begin

if(RSTN)

Rx_data_flag0<=1'b0;

else

Rx_data_flag0<=Rx_data_flag0+1'b1;

end

always@(posedge RSTN or posedge CLK_6_78)

begin

if(RSTN)

Rx_data_flag1<=1'b0;

else

Rx_data_flag1<=Rx_data_flag0;

end

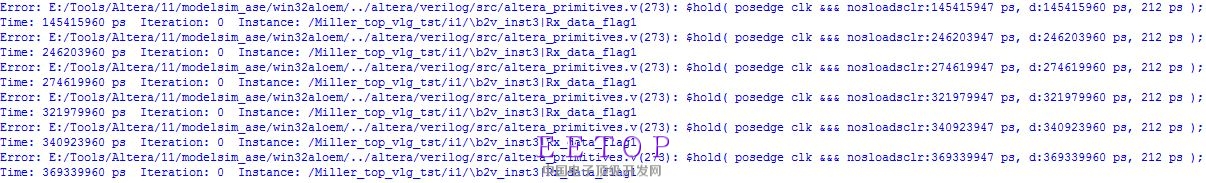

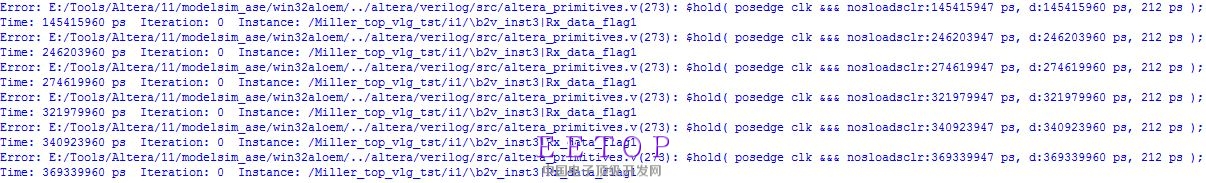

如上代码所示:Rx_data是外部接收到数据,CLK_6_78是6.78MHz时钟。结果门级仿真时就出现下图问题

altera_primitives.v(273): $hold( posedge clk &&& nosloadsclr:145415947 ps, d:145415960 ps, 212 ps );

begin

if(RSTN)

Rx_data_flag0<=1'b0;

else

Rx_data_flag0<=Rx_data_flag0+1'b1;

end

always@(posedge RSTN or posedge CLK_6_78)

begin

if(RSTN)

Rx_data_flag1<=1'b0;

else

Rx_data_flag1<=Rx_data_flag0;

end

如上代码所示:Rx_data是外部接收到数据,CLK_6_78是6.78MHz时钟。结果门级仿真时就出现下图问题

altera_primitives.v(273): $hold( posedge clk &&& nosloadsclr:145415947 ps, d:145415960 ps, 212 ps );