外部逻辑和MicroBlaze交换数据

各位大侠晚上好,在学习vivado过程当中遇到一些问题特来版上请教:

大致流程如这位仁兄差不多,不过他用的是ISE,而我的是vivado,链接如下:

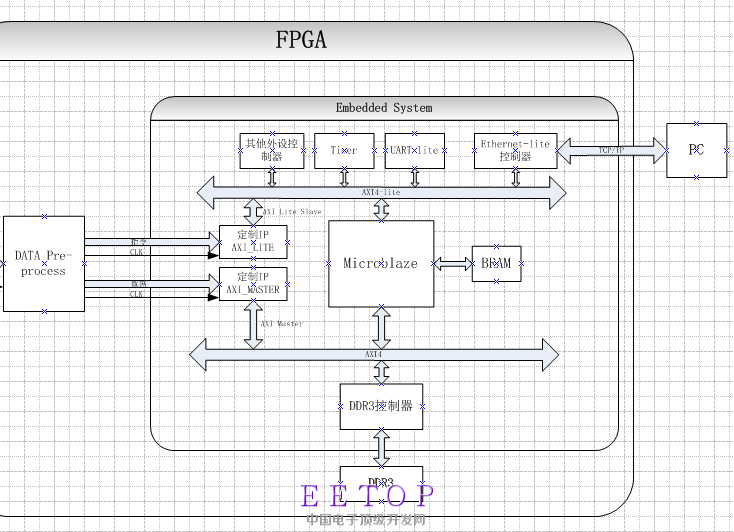

我现在正在使用Digulent 的Arty Development Kit,目前正在做一些学习验证,现在想把本地端的自己产生的数据先存入DDR3,然后由MicroBlaze从DDR3中把数据通过以太网发到计算机中。

我现在的进度是MicroBlaze已经能够从DDR3中读取数据,并且能够通过TCP协议(用Lwip协议栈)发到计算机上,计算机端我用java写了个程序接收数据,数据也能够正常的收到了。

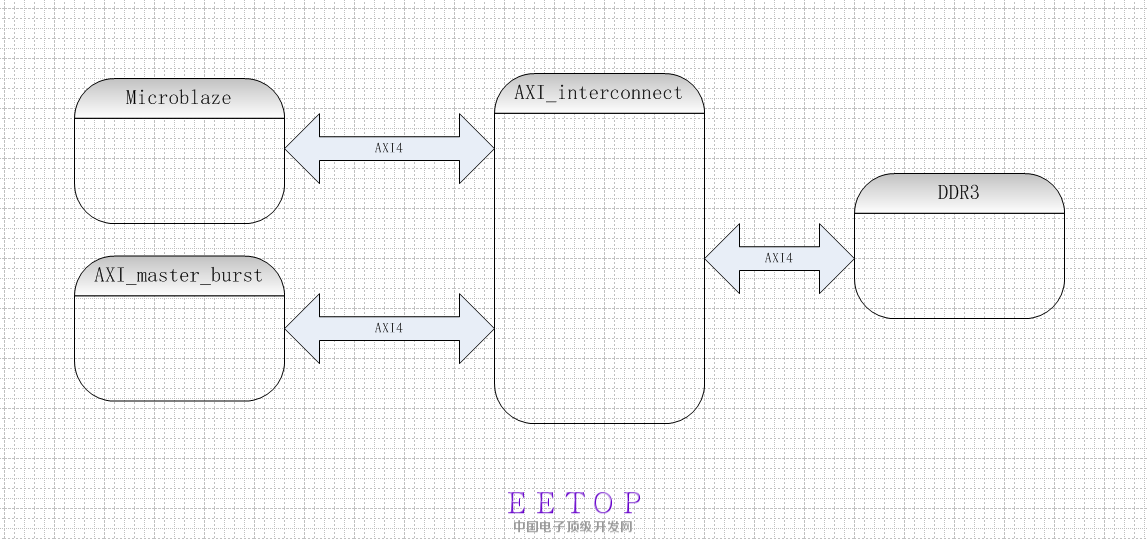

数据这块是用的AXI_MUSTER_burst这个自定义IP,就是自己创建的全功能AXI总线接口模块,定义的是master方式。

目前进展如下:

通过自己建立AXI_LITE_SLAVE的IP通过操作寄存器方式可以和miacoblaze进行指令交互,类似一些开始开始,传输完成等等指令,采用的是axi4_lite。

现在想数据传输采用的axi4协议,根据指令要求将数据写入到DDR3当中,然后写完成后通过指令通知microblaze写完成了,Microblaze就可以读取数据之后通过网口上传,但是目前执行该模块后外部逻辑倒是可以正常测试即写入DDR3之后再读出来,但是Microblaze那边却不运行,即microblaze好像挂掉了,怀疑是不是两个master(一个是microblaze另一个就是axi_master这个模块)因为没有仲裁导致axi_master一直占用axi4总线导致的。

大致框图贴一下吧:

相关axi_master_burst、microblaze与ddr3的连接框图如下:

目前处于将所有模块都加上后竟然一直无法编译过去,一直处于Initializing Design阶段不懂,所以想问一下大神门我这个思路是否正确,或者应该是什么样子的,跪谢啦先!

补充:通过microblaze向DDR3中写的数据可以通过外部逻辑读出且数据正确,经过测试外部逻辑通过axi接口写到DDR3中的数据在Microblaze侧读出的数据不对,还是ddr3中的默认数据,外部逻辑写入和读出没有问题,读写的地址也对,但是软核那边自己读写时正确的,感觉两则之间地址分配没有在一个地方啊,继续查找原因!

自己顶一下吧先,在线等高手解答!

结一下贴

解决:软核程序采用的模板是hello world,如果是memmory test的末班发现就可以测试成功,定位问题到main函数下的init_platform,进入该函数先通过替换helloworld下的platform.c为memory test下的platform.c即可,是里面的定义有问题。