关于Vivado的Implementation Timing Stimulation的问题

时间:10-02

整理:3721RD

点击:

大家好

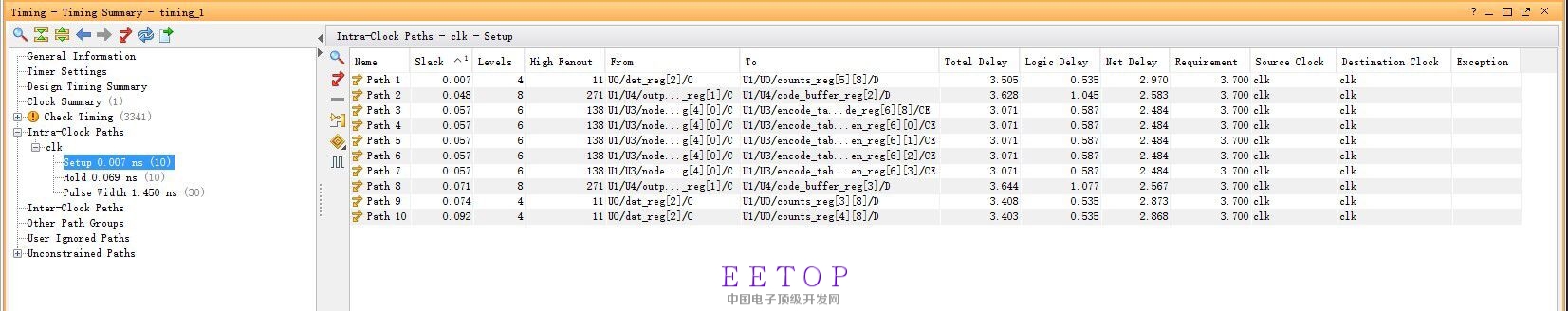

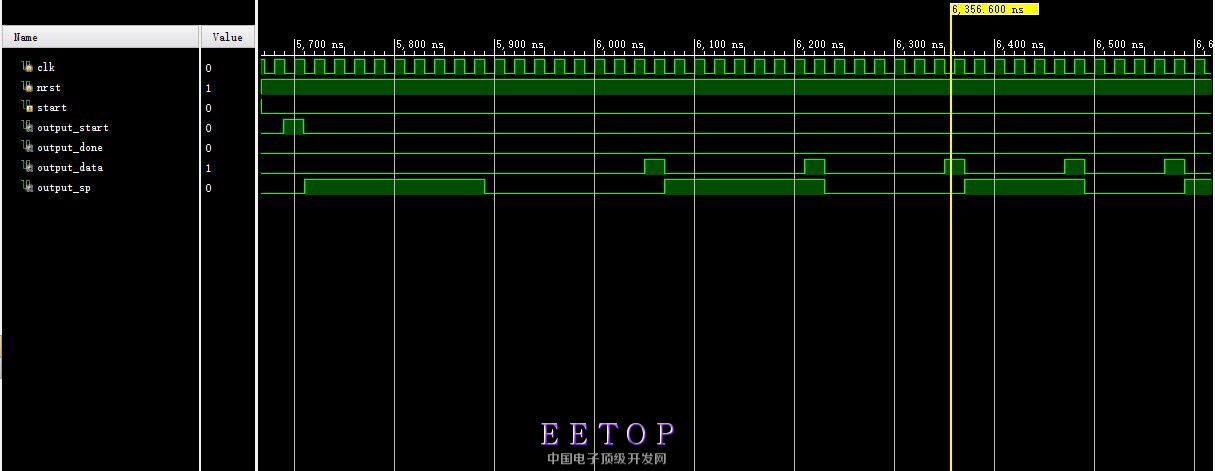

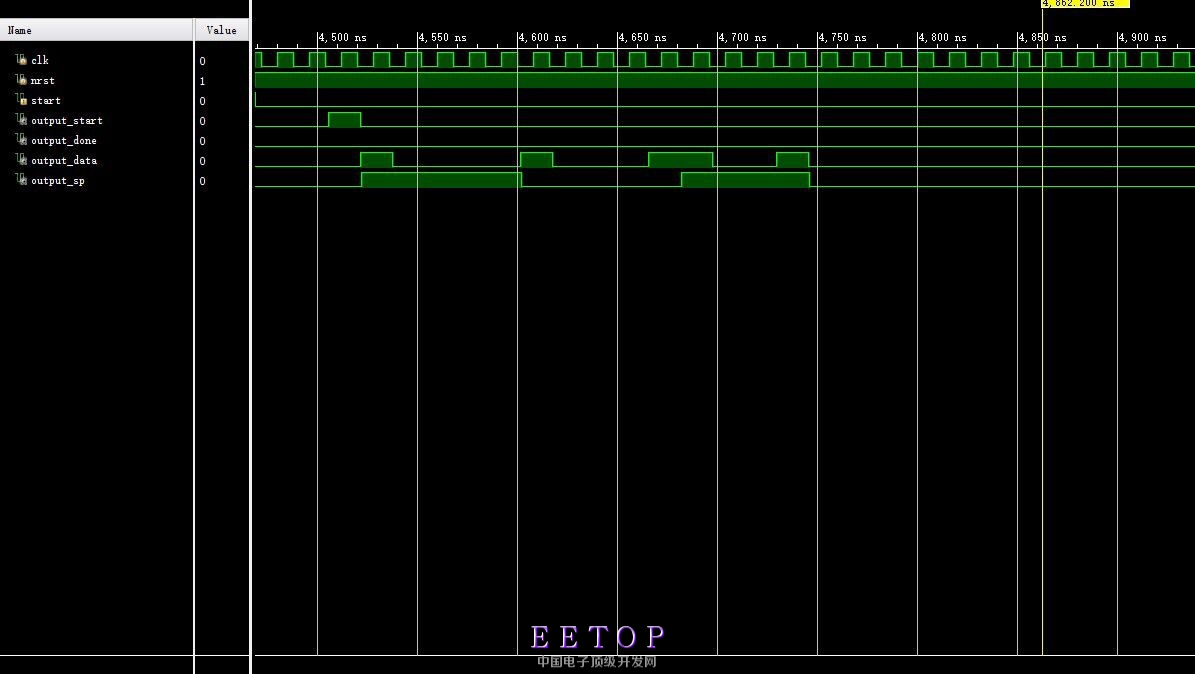

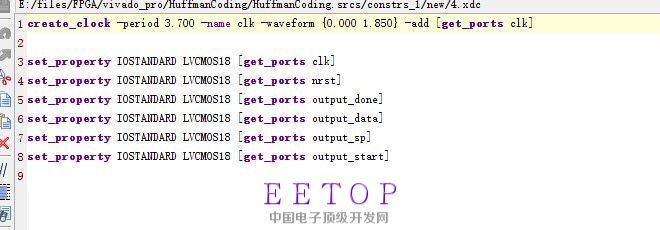

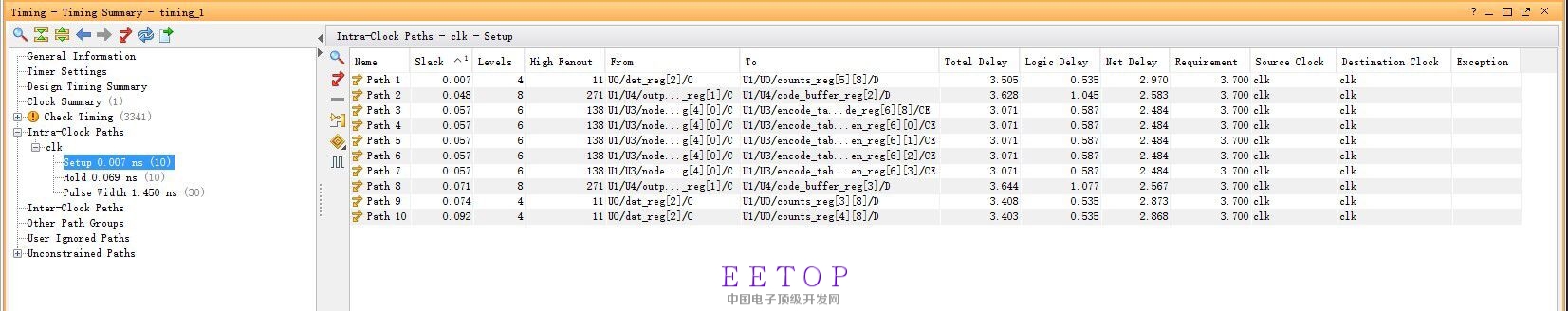

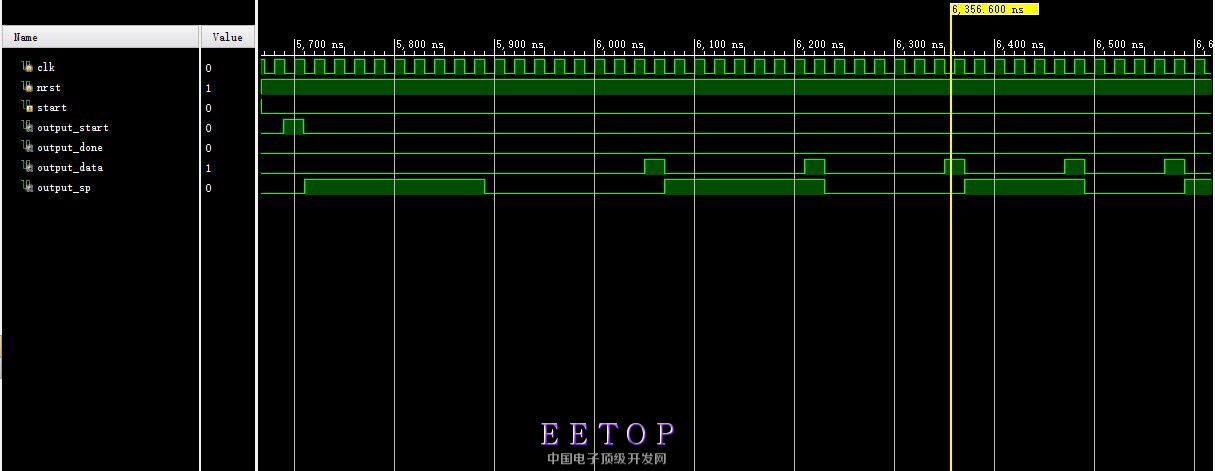

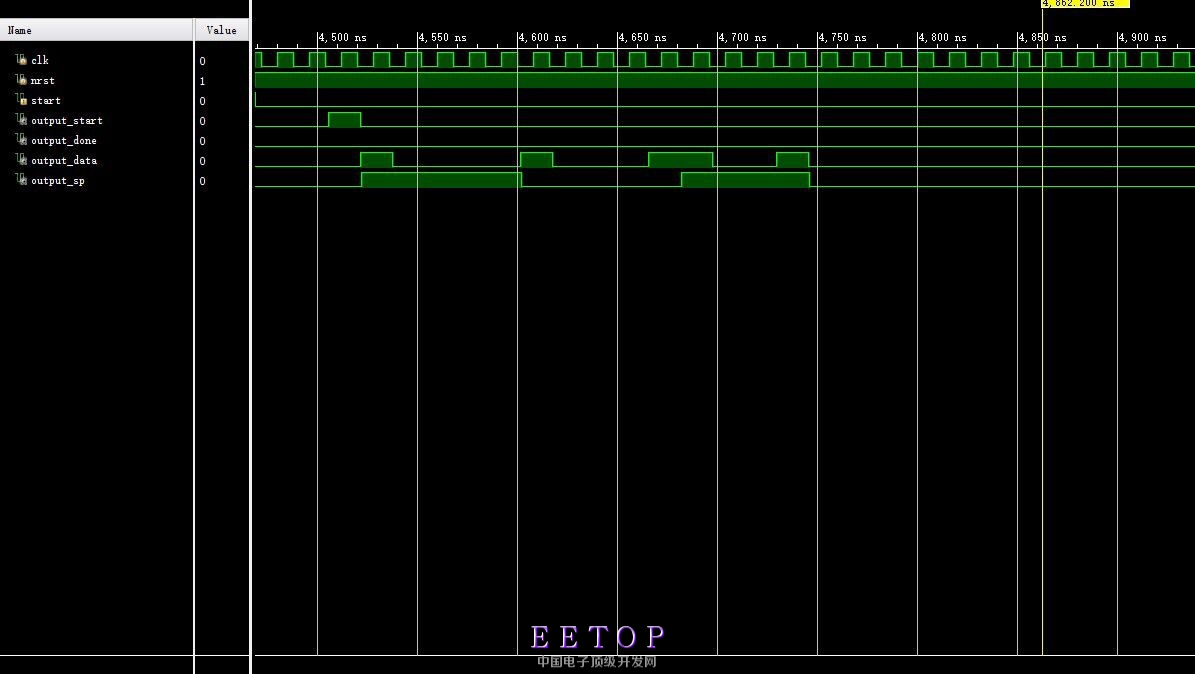

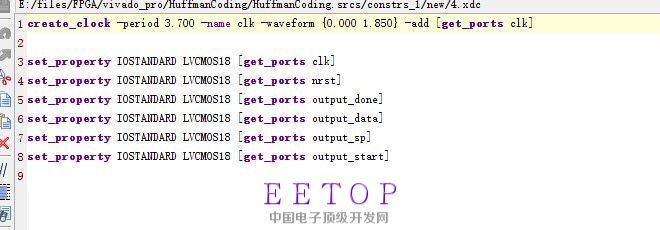

我在用Vivado做一个FPGA模块设计,进行到了后仿阶段,遇到了Implementation Timing Stimulation时没有波形或者波形错误的问题。时序分析如下图,没有报错。 接下来两张图是Implementation Timing Stimulation时,频率分别设置为50MHz和66MHz时的波形图,50MHz时是正确的,但是到了66MHz就变成错误的波形了,至于到了200MHz就连波形都没有了(因为时序分析显示关键路径为3.7ns,我期望这个模块能跑到200MHz)。最后一张图是我时序分析时用的XDC约束文件。

想向大家请教发生这个问题的原因是什么?是软件使用方面的问题还

时序分析:

50MHz:

66MHz:

XDC约束:

我在用Vivado做一个FPGA模块设计,进行到了后仿阶段,遇到了Implementation Timing Stimulation时没有波形或者波形错误的问题。时序分析如下图,没有报错。 接下来两张图是Implementation Timing Stimulation时,频率分别设置为50MHz和66MHz时的波形图,50MHz时是正确的,但是到了66MHz就变成错误的波形了,至于到了200MHz就连波形都没有了(因为时序分析显示关键路径为3.7ns,我期望这个模块能跑到200MHz)。最后一张图是我时序分析时用的XDC约束文件。

想向大家请教发生这个问题的原因是什么?是软件使用方面的问题还

时序分析:

50MHz:

66MHz:

XDC约束:

器件为xc7vx485tffg1157-1