门控时钟中DFF应该下降沿触发还是上升沿触发?

时间:10-02

整理:3721RD

点击:

最近被一个简单的问题的疑惑到了。一个资料上写到:

门控时钟一般怎么实现?

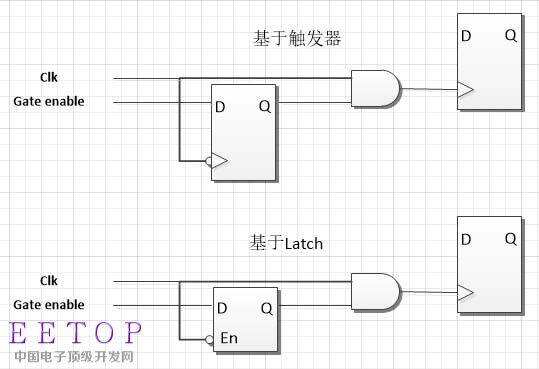

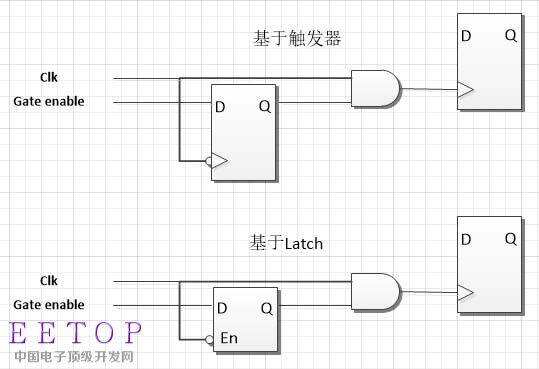

通常是在时钟树上插入门控单元。经典的结构是这样的:对于上升沿有效的系统时钟clk,他的下降沿先把门控使能信号打一拍,然后再用这个使能信号和系统时钟clk相与后作为后续电路的门控时钟。这样的门控时钟电路很好的解决了组合逻辑常见的一些问题。它避免了毛刺的出现,同时也有效的抑制了亚稳态可能带来的危害。门控时钟电路图如下:

我的问题是: 为什么使用下降沿设计可以初步避免组合逻辑的毛刺呢?

我的理解是:难道不应该是上升沿设计才能避免gate enable信号和clk时钟信号不是往相反的方向变化,从而才能避免毛刺吗?

甚是不解,求解答,谢谢了!

门控时钟一般怎么实现?

通常是在时钟树上插入门控单元。经典的结构是这样的:对于上升沿有效的系统时钟clk,他的下降沿先把门控使能信号打一拍,然后再用这个使能信号和系统时钟clk相与后作为后续电路的门控时钟。这样的门控时钟电路很好的解决了组合逻辑常见的一些问题。它避免了毛刺的出现,同时也有效的抑制了亚稳态可能带来的危害。门控时钟电路图如下:

我的问题是: 为什么使用下降沿设计可以初步避免组合逻辑的毛刺呢?

我的理解是:难道不应该是上升沿设计才能避免gate enable信号和clk时钟信号不是往相反的方向变化,从而才能避免毛刺吗?

甚是不解,求解答,谢谢了!

时钟下降沿之后电平为低,时钟控制信号在下降沿tco后才输出,因此与逻辑之后时钟到寄存器还是低电平。不会有毛刺。

大概是明白了,谢谢!问下那触发器类型的门控时钟和锁存器类型的门控时钟有什么区别呢?

Latch类型的时序松一点

谢谢了、、、