插值器和抽取器用VHDL怎么实现?

时间:10-02

整理:3721RD

点击:

FPGA中的插值器和抽取器用VHDL怎样实现呢?

抽取,比如4倍抽取,就做个模4计数器,计满采一次样;

插值,我知道的分插0跟复制,如果插0的话,就是在高时钟下补0,复制的话,就是复制前一个值,别的不知道了

有没有懂得的知道一下?对这个完全没有头绪

插值和抽取是利用滤波器实现还是?

当然需要滤波器,找本多速率信号处理的书看看

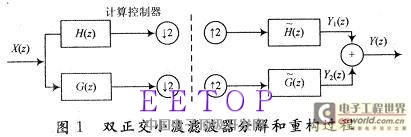

我也了解了一些多采样率滤波器方面的知识,只是在这样一个滤波器组中,上面是低通,下面是高通,中间的抽取器和插值器也是用滤波器实现吗?谢谢

那就不需要了啊,两头不是已经做了滤波器了吗?下采样前加滤波器抗混叠,上采样后加滤波器去掉镜像

抽取,多个数相加得出一个数?

那中间的那个上下采样怎么实现啊?是用VHDL写还是怎么的?我对这个完全一头雾水,不知道该怎么去实现它,,求指导

直接说抽取就是2个里面留1个,具体设计应该和前面的滤波器结合起来,这个说来话长了,自己找书看去吧