求:非阻塞赋值没有延时或只有半个周期延时,这是什么原因造成的?

时间:10-02

整理:3721RD

点击:

求:非阻塞赋值没有延时或只有半个周期延时(在测试代码中改变clk的初值),这是什么原因造成的?理论上非阻塞赋值不是应该延时一个clk时钟吗?非阻塞赋值在always@(posedge clk)中always @(posedge clk)

a<=b;

[attach]687338[/attach]

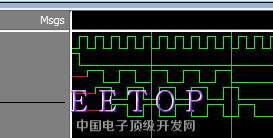

clk初值为0时,赋值无延时

[attach]687337[/attach]

clk初值为1时,赋值延时半个时钟

你最好将代码和仿真波形贴出来,不然别人给你怎么看。其实我不会

有代码么?

例如:

always@(posedge clk) a<=b;

出现下图两种情况:

[attach]687338[/attach]

clk初始值为0时,赋值无延时

[attach]687337[/attach]

clk初始值为1时,赋值有半个时钟延时

例如:

always@(posedge clk) a<=b;

出现下图两种情况:

[attach]687338[/attach]

clk初始值为0时,赋值无延时

[attach]687337[/attach]

clk初始值为1时,赋值有半个时钟延时

你好像贴的是假的图片

不知道我理解的是不是你说的,modelsim仿真做的是功能仿真,所以它忽略的本级寄存器从D-Q的数值传输延时,而且输入信号必须是wire类型,net delay也是忽略不计的,所以在时钟上升沿数据直接被传输的b_o端口,但非阻塞赋值在两个寄存器传输之间是有效果的,b_o和c_o。中间差出一个时钟周期,你所说的差出半个时钟周期我觉得就是上面这种情况,是你testbench的问题,下降沿开始赋值要等到上升沿才能被采到。你的代码没有源码么,而且图片也看不见。

哈哈,编辑插入图片提示服务器出错,没办法咯

你的理解是对的,谢谢您

必须支持一下