inout仿真问题

时间:10-02

整理:3721RD

点击:

参考了如下的方法:

<http://bbs.eetop.cn/thread-24583 ... page%3D1&page=1

仿真图如下所示

[attachimg]685931

[attachimg]685931

[/attachimg]

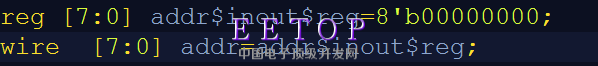

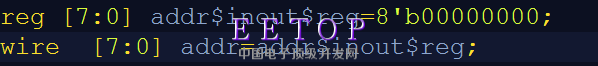

addr$inout$reg 用来写数据

addr用来读数据

先向地址0x00 写入0x09 再向地址0x1f写入0x09 最后读取地址0x1f的值。

如图中箭头所示,addr的状态为红色即为未知。而程序中的inout的端口是这样定义的:

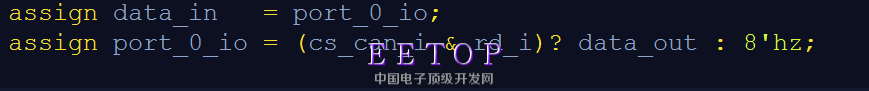

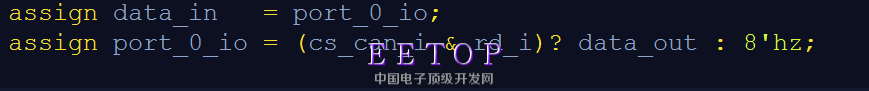

在testbench中将addr传给port_0_io端口。

那么在读的时候cs和rd同时为高时,addr的数据不是应该是data_out的数据吗?为什么会是未知值呢?

http://bbs.eetop.cn/thread-246972-1-1.html

eetop上面也有遇到这个问题的,但是给出的解决方案是编译源文件,我试了,依然不好使。求教啊,,大神们帮忙看看呀。

<http://bbs.eetop.cn/thread-24583 ... page%3D1&page=1

仿真图如下所示

[attachimg]685931

[attachimg]685931[/attachimg]

addr$inout$reg 用来写数据

addr用来读数据

先向地址0x00 写入0x09 再向地址0x1f写入0x09 最后读取地址0x1f的值。

如图中箭头所示,addr的状态为红色即为未知。而程序中的inout的端口是这样定义的:

在testbench中将addr传给port_0_io端口。

那么在读的时候cs和rd同时为高时,addr的数据不是应该是data_out的数据吗?为什么会是未知值呢?

http://bbs.eetop.cn/thread-246972-1-1.html

eetop上面也有遇到这个问题的,但是给出的解决方案是编译源文件,我试了,依然不好使。求教啊,,大神们帮忙看看呀。

inout类型的仿真可以参考一下这篇博文http://blog.chinaaet.com/weiqi7777/p/35914,亲测可用

我晕手机打半天的东西没了,代码就不写了,说说我的一个方法。

在被测文件是“输入输出”,在测试文件就要“输出输入”。如果实际使用没问题,仿真出现未知态,可能是输入输出转换控制没有对应出现了空档,或者是相冲突。

我的偷懒方法是在测试文件中设一个大计数器,从开始计数,跑一遍,知道被测代码中io口控制转换的cnt值,然后在测试文件中“精确”控制io的使能开启