请问上采样在数字电路中怎么实现啊

时间:10-02

整理:3721RD

点击:

请问上采样和下采样在一个数字电路中怎么实现?

上采样和下采样在一个数字电路中?

不清楚你的问题。

如果上下采样的倍数是一样的,应该可以复用乘法器

我能理解为你想做一个能上升沿采样也能下降沿采样的电路么

bunan

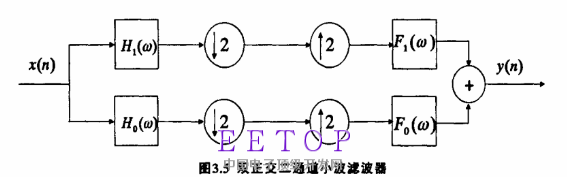

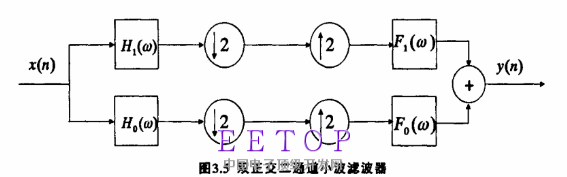

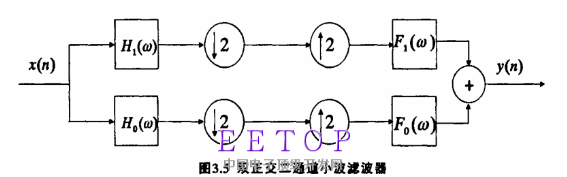

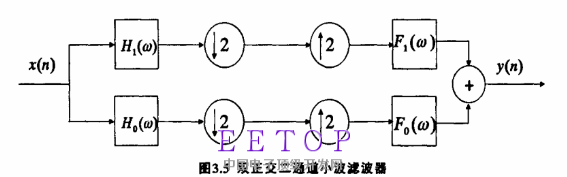

就是一个滤波器组,里面涉及到了上采样和下采用,如图所示,我要用VHDL语言来设计,但不懂中间的上下采样应该怎么实现?

这叫插值 、抽取,XILINX的FIR IP核带这功能

下采样就是抽取,要保证不失真;

上采用就是内插,也要保证不失真;

保证不失真的话:

下采样一般是先滤波后抽取,H1可能就是滤波器;

上采样一般是先内插后滤波,F1可能也是滤波器。

我觉得他要问的是不是怎么上下沿都采样 因为触发器不能上升沿下降沿都采样吧

这里和边沿采样应该没有关系,小编所问的东西已经由其给出的图片表示了,实现的是滤波功能,这里可能是数字信号处理相关的内容(可能是图像处理),和算法相关。

对,我是研究算法,然后通过建模实现这样一个滤波器组电路,整个电路中有4个滤波器,中间需要经过一个下采样和上采样,我对这个采样的实现不太懂,是通过FPGA设置还是用VHDL语言设计怎么的?谢谢

学习一下

VHDL设计。

就是说我需要用VHDL语言设计两个单独的采样模块?

不知道你纠结几个模块的原因;先把功能实现吧。从你给出的图,简单说,你可以做4个模块;两个通路复用这4个模块。

至于模块框架,发扬良好规范的风格,结合自己的喜好;

具体的可能我也不太懂,我也是FPGA小白一个