SSRAM时序

时间:10-02

整理:3721RD

点击:

图1

图1

图2

1.想问下有人用过SSRAM 吗,对于这个时序图我也是奔溃的,看不懂啊,

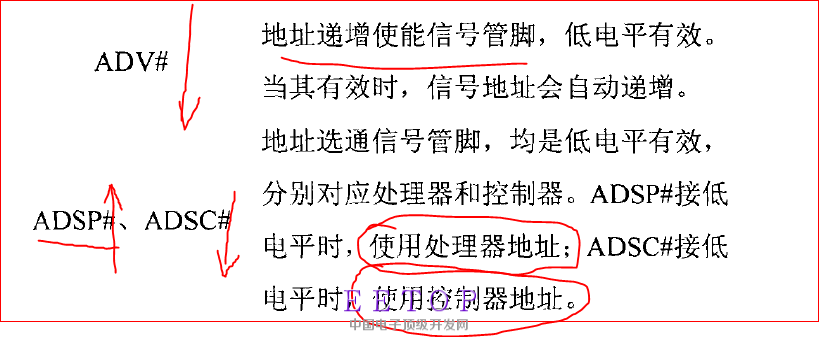

2.还有就是图一中我所标记的部分所说的问题,地址自增是什么意思?(还需要我写地址产生模块吗?)

3.处理器地址和控制器地址分别指的什么?

4.我需要的是连续读写,看的大多都不是连续读写的

如果PCB布线可以, adsc接低,另两拉高,自己产生读写地址即可(注意读有延迟);地址自增、处理器地址和控制器地址与芯片是否工作在突发模式有关,也就是地址A0,A1 由内部产生还是由外部提供,其它类似

这个是ISSI IS61LPS204832/36 的时序图, 32位或36位数据读写的 SSRAM 时序。 存储量还可以,速度很快,实现这个时序不难,信号全是单向的。 一年前已经实现过。 严格按照时序来就对了。

十分感谢,现在硬件上已经做完了,是(ADSC#,ADV#,拉低,ADSP#拉高,)1.你看我这么理解对吗?(控制器地址就是外部给的,处理器地址就是自增?) 2. 现在是控制器地址,(外部给地址),那怎么实现自增呢,我把原理图给你看下。

[attach]685255[/attach]

你帮我看下是什么工作模式?谢谢。

谢谢你,你说的很对,现在我有几个问题能否请教下你,

1.根据原理图能判断是工作在BURST 模式?

2.从图中可以看出地址是外部控制器给的,为什么ADV#还要拉低。

3.我想连续读或是写,而且我看资料说(读需要三个周期,写只需要一个周期),那么怎么能保证读写速度一样?

4.GCLK=160M,GW#=160M,OE#= 160M,那么是不是可以认为读写速度都是160M,

5。能不能加个好友,向您多多学习下,