timequest set_input_delay

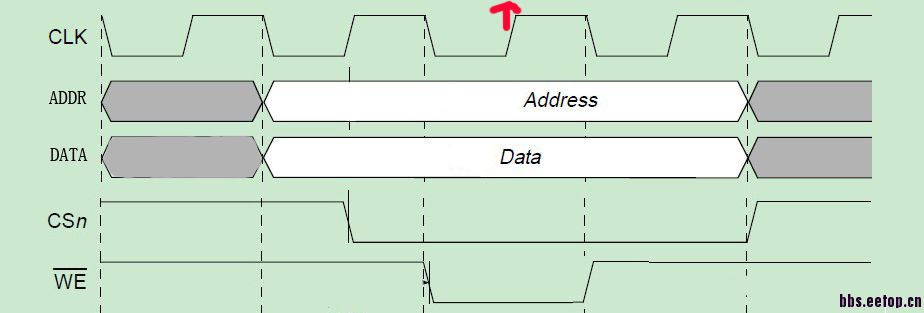

请教一下大家,假设CPU输出如图上信号送到FPGA,FPGA用CLK来采集DATA,如图所示,使用红色箭头的上升沿采数

程序大概如下,假设时钟100MHz

always @(posedge CLK)

if(~WEn & ~CSn)

case(ADDR)

4'h0 : reg0 <= DATA;

4'h1 : reg1 <= DATA;

....

default:;

endcase

我写了相关约束

create_clock -name {CLK} -period 10.000 -waveform { 0.000 5.000 } [get_ports {CLK}]

#设置input_delay

set_input_delay -max 5 -clock CLK [get_ports {WEn}] # 这里的5ns时间并非十分精确,只是说明问题而已

set_input_delay -min 5 -clock CLK [get_ports {WEn}]

由于WEn的有效时间正好是一个周期,这样写是没有问题的,可是其他信号如ADDR,DATA,CSn的input_delay怎么写

呢

其它的可以不写,或者也写成5NS就行,

在使用使能信号时先打两拍,这样更稳定。

这个有多种设法,最简单的一种是(以ADDR为例):

#max下计算setup,比0延时放松5ns,负数方向是放松

set_input_delay -max -5 -clock CLK [get_ports {ADDR*}]

#min下计算hold,比0延时放松15ns,正数方向是放松

set_input_delay -min 15 -clock CLK [get_ports {ADDR*}]

需要指出,你WEn这个是理想情况的例子,真实约束不能出现min=max的情况,需要收紧一点。

另外需要指出,对这种IO有些路径紧有些路径松的情况,综合那一步一定要开物理综合。如这里WEn路径最紧,只有开了物理综合才会使WEn到reg0/reg1的组合路径最短。

好贴!

我就是无法理解这里面的“负”

非常感谢Timme的回答

如果使能WEn打两拍,那是不是其他信号如ADDR DATA CSn也要同时打两拍呢?

如果是这样的话,那还是得保证打第一拍的时候所有信号都能采对才行,这个可以提高稳定性吗,

还是我理解有问题了,望赐教啊

CSn也跟着打两拍,ADDR, DATA你可以看着办,也跟着两拍就好,

其实做不做关系不太大,因为其它几个信号变化都较慢,几个CYCYLE才变化一次,那相对来说,对时序要求并不严格,只要把里面的时序敏感路径重点处理就好。

打两拍算是单BIT信号跨时钟域的常用方式,减少最后输出时slack造成的不稳造成误采,当成通行做法就行,不需要想太多。

你自己上板多测测就行,有些知识点书上会说要多认真处理之类的,而实战时并不需要考虑太多,放松些约束反对其它路径有好处。

好贴 顺便请教下 如果CPU到FPGA的Data总线是双向的,要怎么约束

灌水,升级