计数器,时序

时间:10-02

整理:3721RD

点击:

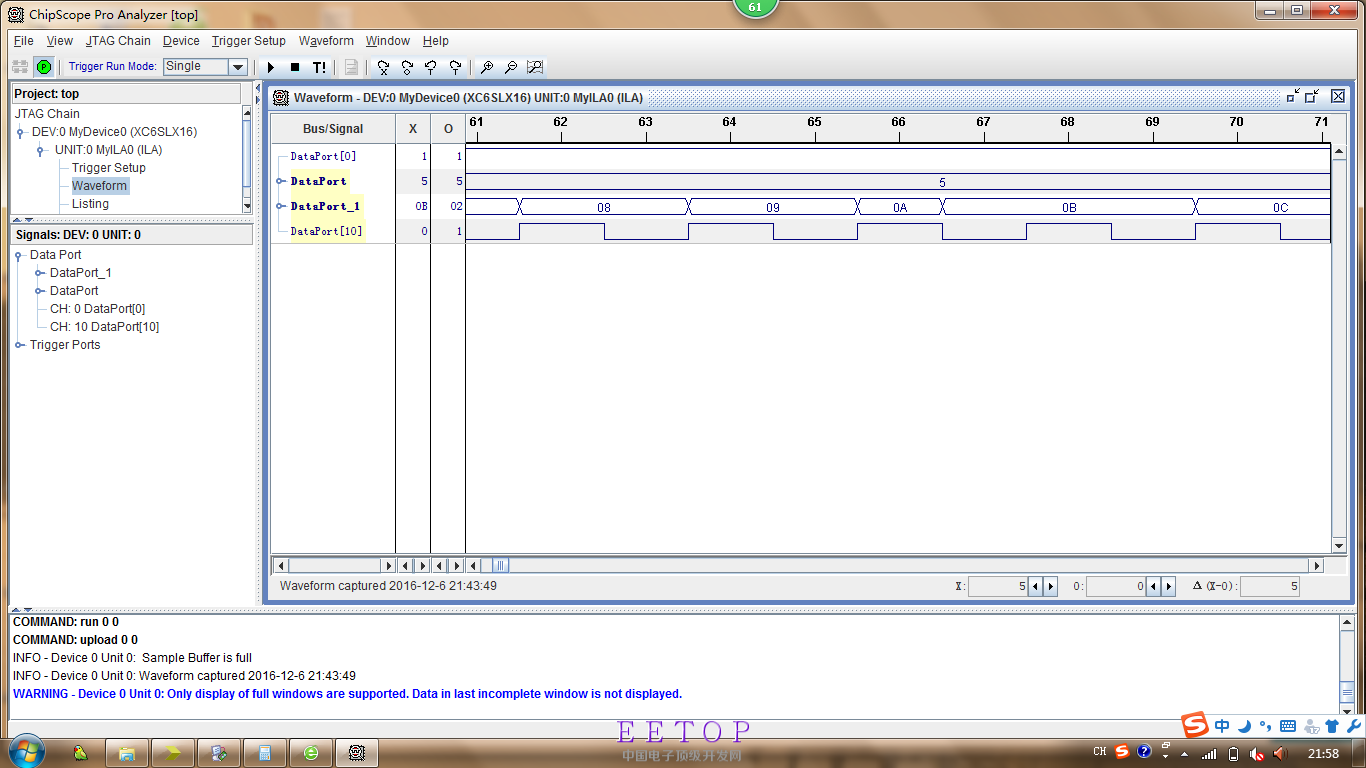

图中DataPort_1是计数器,DataPort[10]是时钟。数据0A结束时刻出现异常,请问出现该现象的原因一般有哪些?

图中DataPort_1是计数器,DataPort[10]是时钟。数据0A结束时刻出现异常,请问出现该现象的原因一般有哪些?

CHIPSCOPE的采样时钟用的哪个?

有某个组合逻辑干扰

检查一下计数器自加的约束条件

如果你的采样时钟不是待采样数据同步时钟的整数倍,那么采样错误是必然的

采样时钟是668M,待采样数据的同步时钟是334M,正好是整数倍关系

不知道你用的什么器件能跑668MHz,时序都收敛了?

668M?牛

668M是chipscope 采样用的,内部的全局时钟是334M,?

全跑乱了 DDR3

DDR3 核不会用

你看一下STA报告,我认为时序是不可能收敛的

不动啊

这种情况一般是HOLD违例,遇到过这种情况

remove the clk

nice,收藏了,很好

频率不可能那么高吧