在ISE中初始化ROM遇到的问题(coe和mif文件)

1. 每次想更改初始化文件(.coe)时, 打开IP核,里面的所有参数又恢复默认值,都要重新再配置一遍,好麻烦!

2. 更改coe文件后,打开IP核全部重新配置生成,结果.mif文件并没有更新,why?

(查资料说.mif文件才是最终有效的初始化文件)

我每次都要删掉所有的ROM IP核文件,全部重新生成,浪费时间啊,这样太麻烦了!

据我所知,rom ram fifo之类的ip核都是使用的ngc格式的文件,在ip生成的时候,已经确定了初始化的内容。你可以修改coe mif的文件,不过只是在仿真中可以修改rom的初始值,但是在实际布局布线时是不能修改的。

如果要修改rom的初始值,可以先修改coe中的内容,再用coregen重新生成ip。

不过,有一种解决办法。

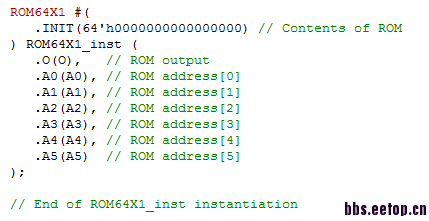

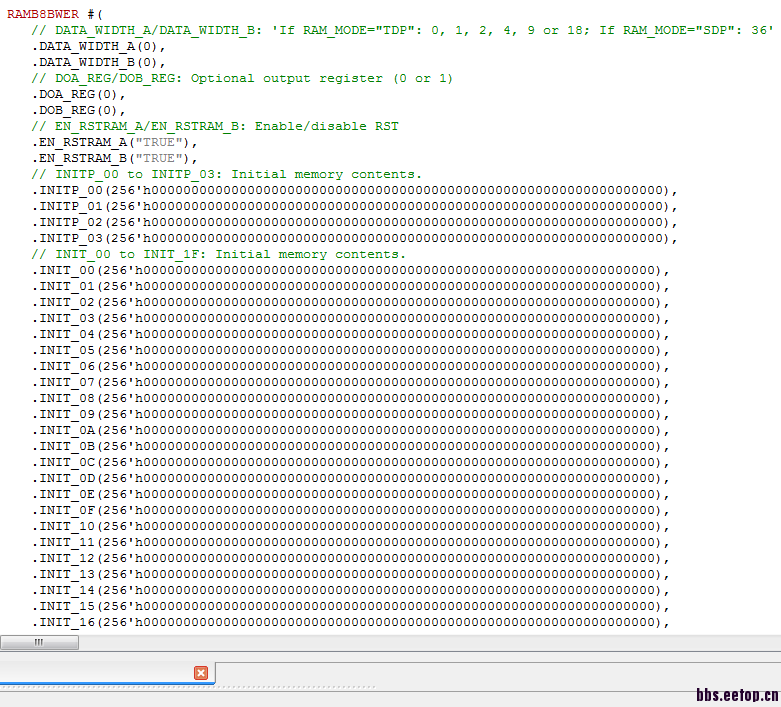

不用coregen的生成ip的方法,自己写rom。

在xilinx里面,可以用分布式ram和block ram生成rom。这两种方式,都可以指定初始化的内容。

不过用这种方法不如coe文件或者mif文件看着直观。

我用的方法是做一个脚本文件,将coe中的内容转换为 分布式ram或者block ram的初始化的值。二楼正解!

当我想要修改ROM的初始化内容,用新的coe文件重新生成ROM的ip核,是不是只要.ngc文件更新了,就说明我的初始化文件已经更新成功了。直接用 vhd/verilog 语言描述 初始化 ram

以我的理解,是的。你可以在ise中只添加ngc文件,也是可以编译通过的

用 rtl 描述存储器,工具在综合的时候,可能会有多种选择,可以用 blockram 分布式ram 或者ff搭建,不好控制coe文件发生了变化,导致IP生成错误,然后就算更改rom设置,rom的设置也会回到最初的。最快的方法,就是先Remove了,再重新生成一下

为什么更改.coe文件后,IP核的生成是错误的?我也遇到过类似的问题:从原工程中复制了一个版本,更改IP核的参数设置,更新.coe文件,点击generate生成成功后,再次对工程进行综合布线,也都没有错误,但是调试时发现rom核里的数据是错误的,再次打开rom核,核的设置竟然变成了初始状态。你知道这是为什么吗?