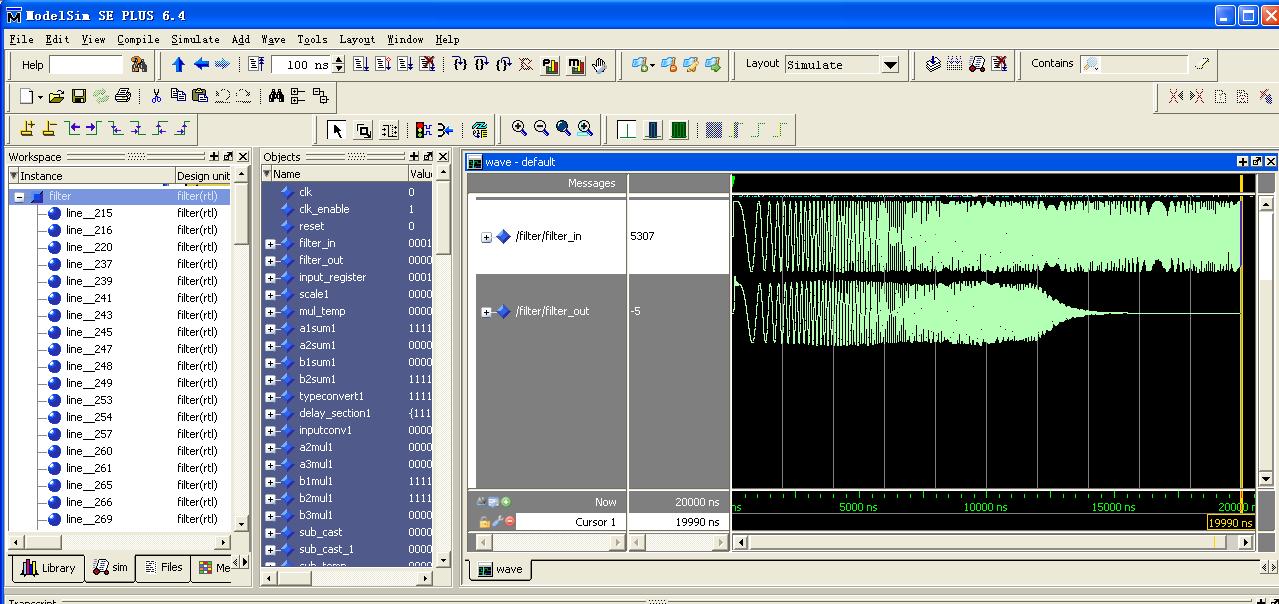

modelsim和matlab仿真出的结果,谁能帮忙解释一下哦。

时间:10-02

整理:3721RD

点击:

本人按照matlab官方网站提供的一个demo设计了IIR低通滤波器。

经过千辛万苦,总算出结果了。

哪个大侠能帮忙分析下下,这结果是怎么解释的呢?

demo的流程在doc文件中,如果感兴趣,可以去这个网站看看哦。

http://www.mathworks.com/products/filterhdl/demos.html

Filter Design HDL Coder 2.4

HDL Filter LinkThis model shows how to use FDATool to

To step through a detailed demonstration of these features, see Step By Step Instructions below. If you prefer to run a quick, automated HDL cosimulation demonstration, see Quick Demo below.

Contents

Demo RequirementsThis demonstration requires

- Mentor Graphics(R) ModelSim(R) (to display analog waveforms, you must have ModelSim SE) simulator - Cadence(R) Incisive(R) simulator

- EDA Simulator Link(TM) MQ - EDA Simulator Link(TM) IN

open_system('hdlfilterlink')Warning: Could not get change notification handle for remoteB:\matlab\test\tools\dsptools.Windows has exhausted its pool of handles for this file server.This server appears to support UNIX-style directory timestamp updates.Type 'help changeNotification' for more info.

Before You BeginBefore you begin the instructions in the following sections, set your working directory to a directory to which you have write access. You must run the model from such a directory; this allows the HDL code to be generated.

Quick DemoYou can run a quick automated cosimulation demonstration using generated VHDL filter code provided with this demo. To run the quick demo:

While the cosimulation is running, click on the Start Simulation icon in the Simulink model and watch the waveforms on the Simulink Time Scope. Use the Autoscale command on the lower scope channel to prove that the difference between the behavioral model in Simulink and the generated VHDL is always zero. Then activate your HDL cosimulator and zoom its waveform viewer to full magnification.

Before you run this model again and start another cosimulation, close your HDL simulator session. You can then rerun the cosimulation (using a different HDL simulator if desired).

Step-by-Step InstructionsDesigning the FilterDouble-click on the blue Open FDATool block in the upper right to start FDATool.

After the FDATool window opens, click on the Design tab and design a direct-form II second-order section filter with the following settings:

You can improve this filter design by rescaling the second order sections to avoid intermediate overflows. Select "Reorder and Scale Second-Order Sections ..." from the FDATool Edit menu. This opens the Reordering and Scaling dialog box. Select the following settings in this dialog box:

Then, click Apply to turn on scaling and click OK to close the dialog box.

Next, quantize the filter as follows:

Note that "Nearest" rounding mode is selected because Simulink does not currently support the default mode, "Nearest (convergent)". The "Nearest (convergent)" and "Nearest" modes differ in the way they treat values whose fractional part is exactly 0.5. In "Nearest" mode, every tie is rounded up in absolute value. In "Nearest (convergent)" mode, the ties are rounded to the nearest even integer.

To verify that the fixed-point settings are correct, select "Magnitude Response Estimate" in the FDATool Analysis menu. Then select "Specification Mask" in the FDATool View menu to overlay a mask and verify that the design meets the specifications.

Generating a Simulink® Model of the FilterThe next step is to generate a Simulink model of the filter. Click the Realize Model icon at the left of the FDATool window. Set the model realization options as follows:

To generate the Simulink model, click the Realize Model button at the bottom of the FDATool window. When model generation completes, a Simulink model containing a subsystem labeled Filter opens.

Open the generated model. Observe that it is constructed from basic elements such as Gain, Sum, and Unit Delay blocks.

Close the generated model.

Generating HDL Code for the FilterSelect 'Generate HDL ...' from the FDATool Targets menu. The Generate HDL dialog box opens. In the Test bench types section of the Generate HDL dialog, deselect the "VHDL file" option. In this demo, the Simulink model contains the testbench, so you do not need to generate VHDL test bench code.

To generate VHDL code for the filter you designed in FDATool, click the Generate button at the bottom of the Generate HDL dialog box.

Cosimulation of the Filter with an HDL SimulatorActivate the hdlfilterlink demo model. The demo lets you cosimulate the generated HDL filter code, using your choice of the following HDL simulators:

To automate the process of setting up and running a cosimulation, this demo provides buttons corresponding to each of these simulators.

To cosimulate with the ModelSim Simulator : Double-click on the blue box labeled for the ModelSim Simulator. This configures the HDL Cosimulation block and then starts ModelSim, which executes a script generated by the m-function hdlfilterlinkcmds.m. ModelSim starts up, compiles the generated VHDL for the filter, runs the vsimulink command to set up for cosimulation, and adds the input and output signals as analog waveforms to the ModelSim waveform viewer.

To cosimulate with the Incisive Simulator : Double-click on the green box labeled for the Incisive Simulator. This configures the HDL Cosimulation block and then starts the simulator, which executes a script generated by the m-function hdlfilterlinkcmds.m. Incisive simulator starts up, compiles the generated VHDL for the filter, sets up for cosimulation, and adds the input and output signals as analog waveforms to its waveform viewer.

Note: If you did not generate VHDL code in the previous step, you can still run a cosimulation. A generated VHDL file (filter.vhd) is provided with this demo. This VHDL file is automatically copied into your local hdlsrc directory if necessary. You can use the Restore filter.vhd button to recopy this file into your local hdlsrc directory when desired.

While the cosimulation is running, click on the Start Simulation icon in the Simulink model and watch the waveforms on the Simulink Time Scope. Use the Autoscale command on the lower scope channel to prove that the difference between the behavioral model in Simulink and the generated VHDL is always zero. Then activate your HDL cosimulator and zoom its waveform viewer to full magnification.

Exiting the Cosimulation ProperlyBefore you run this model again and start another cosimulation, close your HDL simulator session. You can then rerun the cosimulation (using a different HDL simulator if desired).

Going FurtherAfter running this demo once, try changing the Filter Internals rounding mode to "Nearest (convergent)"; then regenerate the VHDL code. Since Simulink does not currently support this rounding mode, "Round to nearest" is used instead in the realized model. However, the VHDL code does implement convergent rounding. Therefore small differences occur between the outputs from Simulink and from the ModelSim cosimulation; these differences will be visible in the lower scope channel.

The Integer Delay block (labeled Hardware Latency in the Simulink diagram) is included in the signal path to model the input and output registers that are generated in the VHDL code. These registers are inserted by default. To disable insertion of these registers in the generated code, click the HDL Options... button in the Generate HDL dialog. Then select the Ports tab and deselect the Add input register and Add output register check boxes. You can also increase the filter latency in the generated code by selecting the Add pipeline registers option in the Generate HDL dialog. In this case, observe the "HDL latency is ... samples" message that is displayed in the MATLAB® command window at the end of HDL code generation. Change the Number of delays parameter of the Integer Delay to equal the latency that is reported in the message.

CADENCE, INCISIVE and the Cadence logo are either trademarks or registered trademarks of Cadence Design Systems, Inc. in the United States and/or other jurisdictions. Cadence's trademarks are used by The MathWorks™, Inc under license.

经过千辛万苦,总算出结果了。

哪个大侠能帮忙分析下下,这结果是怎么解释的呢?

demo的流程在doc文件中,如果感兴趣,可以去这个网站看看哦。

http://www.mathworks.com/products/filterhdl/demos.html

Filter Design HDL Coder 2.4

HDL Filter LinkThis model shows how to use FDATool to

- Design a filter

- Generate a structural model of the filter in Simulink®

- Generate HDL for the filter

- Use an HDL simulator to cosimulate the Simulink behavioral model and the generated HDL

To step through a detailed demonstration of these features, see Step By Step Instructions below. If you prefer to run a quick, automated HDL cosimulation demonstration, see Quick Demo below.

Contents

- Demo Requirements

- Before You Begin

- Quick Demo

- Step-by-Step Instructions

- Designing the Filter

- Generating a Simulink® Model of the Filter

- Generating HDL Code for the Filter

- Cosimulation of the Filter with an HDL Simulator

- Exiting the Cosimulation Properly

- Going Further

Demo RequirementsThis demonstration requires

- One of the following HDL simulators:

- Mentor Graphics(R) ModelSim(R) (to display analog waveforms, you must have ModelSim SE) simulator - Cadence(R) Incisive(R) simulator

- One of the following MathWorks link products, providing a cosimulation interface to the HDL simulator:

- EDA Simulator Link(TM) MQ - EDA Simulator Link(TM) IN

- A directory to which you have write access. You must run the model from such a directory; this allows the HDL code to be generated.

open_system('hdlfilterlink')Warning: Could not get change notification handle for remoteB:\matlab\test\tools\dsptools.Windows has exhausted its pool of handles for this file server.This server appears to support UNIX-style directory timestamp updates.Type 'help changeNotification' for more info.

Before You BeginBefore you begin the instructions in the following sections, set your working directory to a directory to which you have write access. You must run the model from such a directory; this allows the HDL code to be generated.

Quick DemoYou can run a quick automated cosimulation demonstration using generated VHDL filter code provided with this demo. To run the quick demo:

- To cosimulate with the ModelSim Simulator: Double-click on the blue box labeled for ModelSim Simulator. This configures the HDL Cosimulation block and then starts ModelSim, which executes a script generated by the m-function hdlfilterlinkcmds.m. ModelSim starts up, compiles the generated VHDL for the filter, runs the vsimulink command to set up for cosimulation, and adds the input and output signals as analog waveforms to the ModelSim waveform viewer.

- To cosimulate with the Incisive simulator: Double-click on the green box labeled for the Incisive simulator. This configures the HDL Cosimulation block and then starts the Incisive simulator, which executes a script generated by the m-function hdlfilterlinkcmds.m. The Incisive simulator starts up, compiles the generated VHDL for the filter, sets up for cosimulation, and adds the input and output signals as analog waveforms to its waveform viewer.

While the cosimulation is running, click on the Start Simulation icon in the Simulink model and watch the waveforms on the Simulink Time Scope. Use the Autoscale command on the lower scope channel to prove that the difference between the behavioral model in Simulink and the generated VHDL is always zero. Then activate your HDL cosimulator and zoom its waveform viewer to full magnification.

Before you run this model again and start another cosimulation, close your HDL simulator session. You can then rerun the cosimulation (using a different HDL simulator if desired).

Step-by-Step InstructionsDesigning the FilterDouble-click on the blue Open FDATool block in the upper right to start FDATool.

After the FDATool window opens, click on the Design tab and design a direct-form II second-order section filter with the following settings:

- Response Type: select "Lowpass".

- Design Method: select "IIR", "Elliptic".

- Filter Order: select "Minimum order".

- Frequency Specifications: select "Normalized (0 to 1)" in the units field.

- wpass: type "0.48".

- wstop: type "0.52".

- Magnitude Specifications: Select "dB" in the Units field; type "1" in the Apass field and "60" in the Astop field.

- Click the Design Filter button at the bottom of the FDATool window.

You can improve this filter design by rescaling the second order sections to avoid intermediate overflows. Select "Reorder and Scale Second-Order Sections ..." from the FDATool Edit menu. This opens the Reordering and Scaling dialog box. Select the following settings in this dialog box:

- Reordering: select "Auto".

- Scaling: select the "Scale" checkbox.

- Set the scaling selector bar to Linf.

Then, click Apply to turn on scaling and click OK to close the dialog box.

Next, quantize the filter as follows:

- Click the "Set quantization parameters" icon in the left-side of the toolbar. FDATool displays a Filter arithmetic menu in the bottom half of the dialog.

- Select "Fixed-point" from the menu. FDATool displays the first of three tabbed panels of quantization parameters.

- Click the Input/Output tab. Deselect the "Avoid overflow" checkbox, and set input and output fraction lengths to 14.

- Click the Filter Internals tab. Select Round towards Nearest, and set the State fraction length to 14.

- Click the Apply button at the bottom of the dialog.

Note that "Nearest" rounding mode is selected because Simulink does not currently support the default mode, "Nearest (convergent)". The "Nearest (convergent)" and "Nearest" modes differ in the way they treat values whose fractional part is exactly 0.5. In "Nearest" mode, every tie is rounded up in absolute value. In "Nearest (convergent)" mode, the ties are rounded to the nearest even integer.

To verify that the fixed-point settings are correct, select "Magnitude Response Estimate" in the FDATool Analysis menu. Then select "Specification Mask" in the FDATool View menu to overlay a mask and verify that the design meets the specifications.

Generating a Simulink® Model of the FilterThe next step is to generate a Simulink model of the filter. Click the Realize Model icon at the left of the FDATool window. Set the model realization options as follows:

- Block name: 'Filter'

- Select the Overwrite generated Filter block option

- Select the Build model using basic elements option

To generate the Simulink model, click the Realize Model button at the bottom of the FDATool window. When model generation completes, a Simulink model containing a subsystem labeled Filter opens.

Open the generated model. Observe that it is constructed from basic elements such as Gain, Sum, and Unit Delay blocks.

Close the generated model.

Generating HDL Code for the FilterSelect 'Generate HDL ...' from the FDATool Targets menu. The Generate HDL dialog box opens. In the Test bench types section of the Generate HDL dialog, deselect the "VHDL file" option. In this demo, the Simulink model contains the testbench, so you do not need to generate VHDL test bench code.

To generate VHDL code for the filter you designed in FDATool, click the Generate button at the bottom of the Generate HDL dialog box.

Cosimulation of the Filter with an HDL SimulatorActivate the hdlfilterlink demo model. The demo lets you cosimulate the generated HDL filter code, using your choice of the following HDL simulators:

- Mentor Graphics ModelSim Simulator

- Cadence Incisive® Simulator

To automate the process of setting up and running a cosimulation, this demo provides buttons corresponding to each of these simulators.

To cosimulate with the ModelSim Simulator : Double-click on the blue box labeled for the ModelSim Simulator. This configures the HDL Cosimulation block and then starts ModelSim, which executes a script generated by the m-function hdlfilterlinkcmds.m. ModelSim starts up, compiles the generated VHDL for the filter, runs the vsimulink command to set up for cosimulation, and adds the input and output signals as analog waveforms to the ModelSim waveform viewer.

To cosimulate with the Incisive Simulator : Double-click on the green box labeled for the Incisive Simulator. This configures the HDL Cosimulation block and then starts the simulator, which executes a script generated by the m-function hdlfilterlinkcmds.m. Incisive simulator starts up, compiles the generated VHDL for the filter, sets up for cosimulation, and adds the input and output signals as analog waveforms to its waveform viewer.

Note: If you did not generate VHDL code in the previous step, you can still run a cosimulation. A generated VHDL file (filter.vhd) is provided with this demo. This VHDL file is automatically copied into your local hdlsrc directory if necessary. You can use the Restore filter.vhd button to recopy this file into your local hdlsrc directory when desired.

While the cosimulation is running, click on the Start Simulation icon in the Simulink model and watch the waveforms on the Simulink Time Scope. Use the Autoscale command on the lower scope channel to prove that the difference between the behavioral model in Simulink and the generated VHDL is always zero. Then activate your HDL cosimulator and zoom its waveform viewer to full magnification.

Exiting the Cosimulation ProperlyBefore you run this model again and start another cosimulation, close your HDL simulator session. You can then rerun the cosimulation (using a different HDL simulator if desired).

Going FurtherAfter running this demo once, try changing the Filter Internals rounding mode to "Nearest (convergent)"; then regenerate the VHDL code. Since Simulink does not currently support this rounding mode, "Round to nearest" is used instead in the realized model. However, the VHDL code does implement convergent rounding. Therefore small differences occur between the outputs from Simulink and from the ModelSim cosimulation; these differences will be visible in the lower scope channel.

The Integer Delay block (labeled Hardware Latency in the Simulink diagram) is included in the signal path to model the input and output registers that are generated in the VHDL code. These registers are inserted by default. To disable insertion of these registers in the generated code, click the HDL Options... button in the Generate HDL dialog. Then select the Ports tab and deselect the Add input register and Add output register check boxes. You can also increase the filter latency in the generated code by selecting the Add pipeline registers option in the Generate HDL dialog. In this case, observe the "HDL latency is ... samples" message that is displayed in the MATLAB® command window at the end of HDL code generation. Change the Number of delays parameter of the Integer Delay to equal the latency that is reported in the message.

CADENCE, INCISIVE and the Cadence logo are either trademarks or registered trademarks of Cadence Design Systems, Inc. in the United States and/or other jurisdictions. Cadence's trademarks are used by The MathWorks™, Inc under license.

关注中,这个FDAtool生成的HDL code到底好用不呢?是不是可以拿来综合的代码呢?

看来没有人关注

我自己来回答一下吧

是前面的signal from space不断产生频率随时间增加的信号,当达到低通滤波器的截止频率时,后面的高频部分的信号被全部滤除。

看来没有人关注

我自己来回答一下吧

是前面的signal from space不断产生频率随时间增加的信号,当达到低通滤波器的截止频率时,后面的高频部分的信号被全部滤除。

That's all。

好贴子,我也跟一贴

鲜花 北京鲜花 北京花店 北京鲜花 上海做网站

there're anyone have link for incisive module! seem to cosim with modelsim!

我认为设置好的话应该可以~

看生成的程序比较规范

不错的资料

page no found