关于I2C测试里面的上拉问题

时间:10-02

整理:3721RD

点击:

写了一个master模块,与EEPROM挂在了一条SDA线上,两个device的输出都是开漏的三态门。

写testbench时遇到了pullup的问题。个人认为直接在testbench里加一个pullup即可,但是波形出来高电平时为不定态。

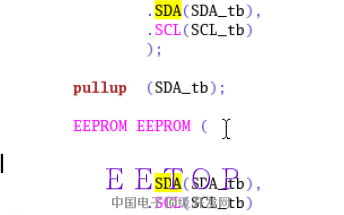

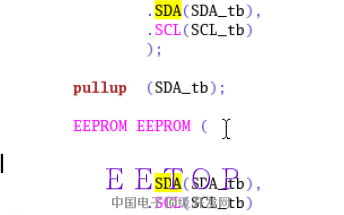

代码这么写的。

代码这么写的。

分开测试两边都是上拉至1,但是一起一仿真就是不定态了。

我没接触过pullup这个标准单元,不知道例化时的用法。恳请各位大神给我指点迷津。

这是我在master里面对SDA线的定义。

EEPROM是现成的模型。

tb里面的SDA是wire型,也不可能赋值。

想问一下是不是两个开漏的三态门是不是不能拉到同一个上拉电阻上,造成了不定态。

写testbench时遇到了pullup的问题。个人认为直接在testbench里加一个pullup即可,但是波形出来高电平时为不定态。

代码这么写的。

代码这么写的。分开测试两边都是上拉至1,但是一起一仿真就是不定态了。

我没接触过pullup这个标准单元,不知道例化时的用法。恳请各位大神给我指点迷津。

pullup 没问题, eeprom如果是现成的模型,应该也不会错

那么就是你的SDA逻辑错了,SDA 高的状态是释放总线到high Z得到的,你是不是直接赋值了?

这是我在master里面对SDA线的定义。

EEPROM是现成的模型。

tb里面的SDA是wire型,也不可能赋值。

想问一下是不是两个开漏的三态门是不是不能拉到同一个上拉电阻上,造成了不定态。

我仿真的时候好像没有用上拉电阻,看起来也是你这个样子,是不是上拉代码有问题?(原来有上拉代码,学习了)

如果没用上拉的话,是怎么让他到高电平的呢.困扰了好久~

我看到的也是红线X态,但是我自动把X当成1了,因为是上拉嘛,所以我的SCL和SDA只有X态和0态,不会出现1,我就无所谓上拉不上了了

slave看到了x后能正确的给出ack信号吗?

ACK是0啊,我不管是master还是slave,从来不主动输出1,只输出0和X。所以ACK就是0啊,NACK就是1。

buff 不就等于直接驱动了么。 i2c 是没有直接驱动到1这个动作的,所以当你sda想要等于1的时候,是靠pull up register 做到的

不用buff驱动的话要怎么拉低这条线呢,不太明白这一块。

EEPROM只有一根inout线,master要能拼起来不也是用一根比较合理吗

问题略着急,求大神解答

已解决!

还是自己蠢了,tb里面忘了加timescale。

无比的希望能够呵呵自己一脸