求助一个K7+DDR3的问题

时间:10-02

整理:3721RD

点击:

我们用XC7K325TFF667自己设计了一块板卡,上面挂了两片DDR3(MT41K256M16HA-125),两片分别为16位数据线,组成32位使用,其他的时钟线、地址线和控制信号线等全部并联。

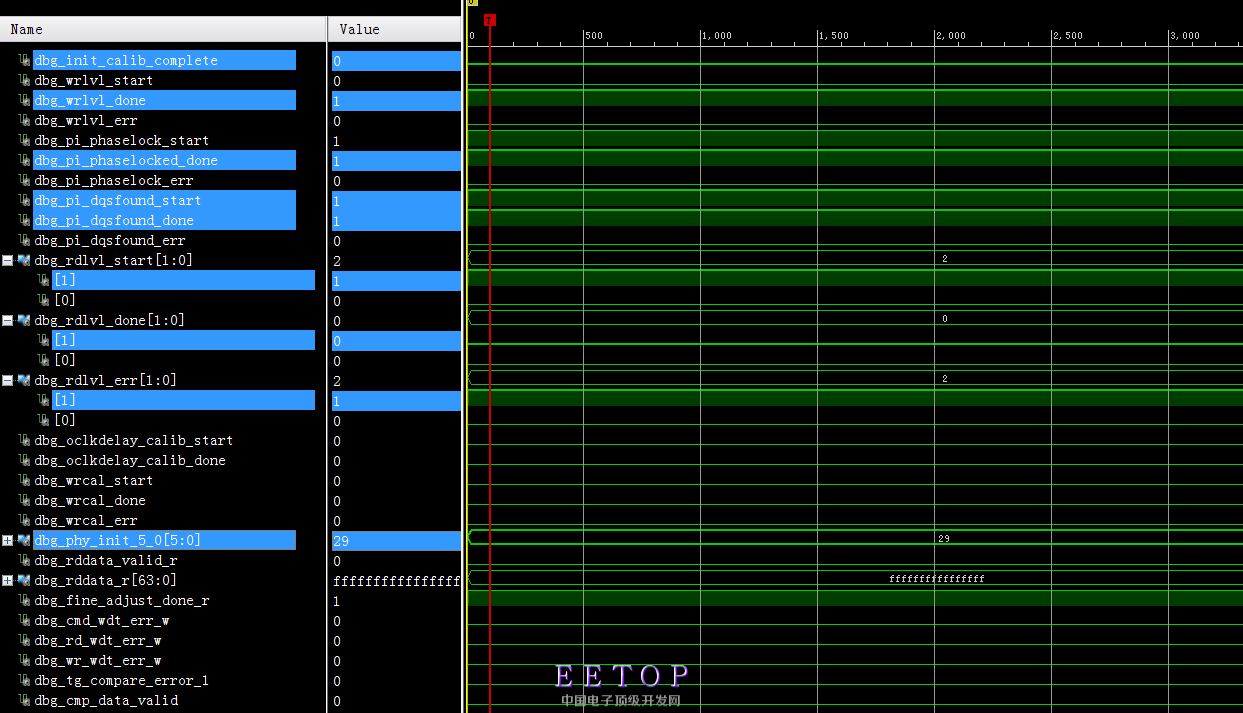

现在用Vivado2015.3自带的DDR3控制器MIG,及其example程序生成了一个最基本的DDR3测试程序。下载后,init_cali_complete信号一直没有变高,使用Hardware Manager查看FPGA内部信号,发现wrlvl_done、pi_phaselocked_done、pi_dqsfound_done均为1,而rdlvl_done[1]是0,rdlvl_err[1]为1,phy_init_5_0[5:0]为6’h29,查询xilinx资料(Xilinx Answer 43879),上述信号表明,在MPR read leveling时出错了。

已排除管脚分配不正确等低级错误,MIG中的各种设置参数也几乎全都试过了。已经在此处困扰了一个月了,求高手们帮忙分析下,问题可能出在哪里?

现在用Vivado2015.3自带的DDR3控制器MIG,及其example程序生成了一个最基本的DDR3测试程序。下载后,init_cali_complete信号一直没有变高,使用Hardware Manager查看FPGA内部信号,发现wrlvl_done、pi_phaselocked_done、pi_dqsfound_done均为1,而rdlvl_done[1]是0,rdlvl_err[1]为1,phy_init_5_0[5:0]为6’h29,查询xilinx资料(Xilinx Answer 43879),上述信号表明,在MPR read leveling时出错了。

已排除管脚分配不正确等低级错误,MIG中的各种设置参数也几乎全都试过了。已经在此处困扰了一个月了,求高手们帮忙分析下,问题可能出在哪里?

问题解决了,但是没想明白是怎么回事。

FPGA的PROG_B管脚还连到别的地方去了,将其断开,DDR3就能正常初始化了。