关于ddr3 mig仿真用户控制接口时序的疑问

时间:10-02

整理:3721RD

点击:

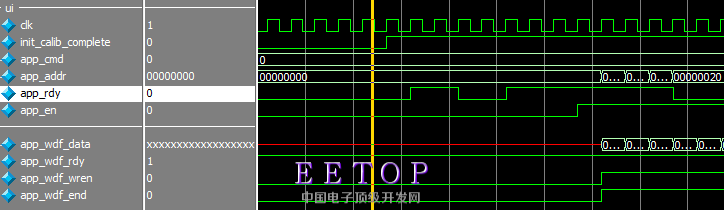

正常情况不是在上电initial and calibrate之后用户就可以直接利用app接口进行读写了吗?使用IP CORE生成的example design的sim工程仿真波形发现在init_calib_complete拉高之后,app_en信号经过一段时间之后才置高,在此期间app_rdy经历拉高拉低再拉高的过程,为何不在rdy第一次拉高之后en就置为有效?难道是在write命令下发前还有别的操作吗,电阻校准、write leveling之类的不是在上电之后就做完了吗?如下图

请高手赐教~