cyclone V DDR3 读写错误

时间:10-02

整理:3721RD

点击:

求助个问题,困扰了好久。

新做的板子,镁光的DDR3 芯片,16位的,发现读写数据时出现数据位跳变错误。

更新:现在发现可能是DDR保存数据的问题,数据在DDR里存储了一段时间后读出,会有部分数据错误,如果存进DDR后立马读出,数据不出错。有遇到过这种情况的吗,是硬件的设计问题,还是DDR得质量问题?

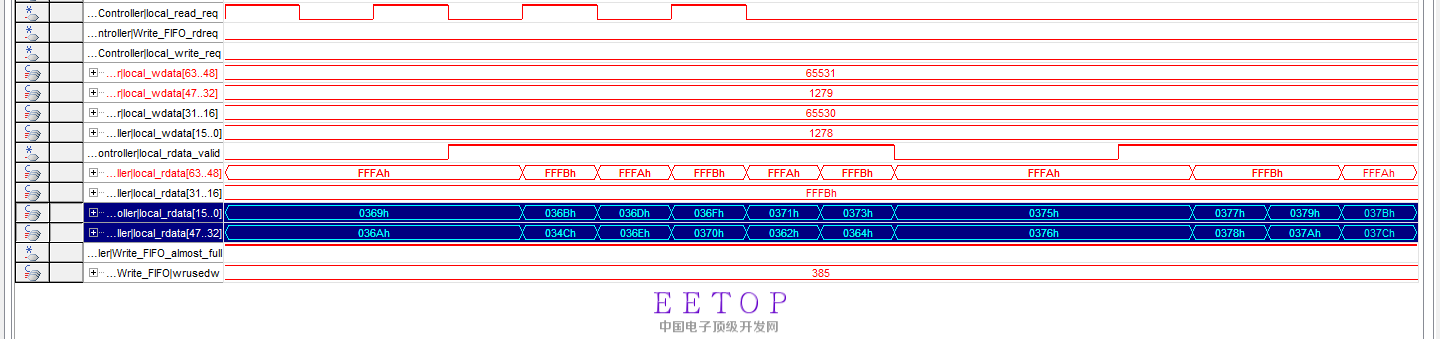

比如写入连续的数据。看下面这张图,从DDR里读出的,数据出错,红色显示的是出错的数据,如下。

数据是16进制显示:

正确的数据应为:369 36A 36B 36C 36D 36E 36F 370 371 372 373 374 375 376

读出的数据变成:369 34A 36B 36C 36D 36E 36F 370 371 362 373 364 375 376

中间的 6 从4’b0110 变成4'b0100

7 从4'b0111 变成 4'b0110

请问发生这种情况问题一般出在哪里?谢谢~

.....

DDR 的时序全部收敛,问题依然没有解决

三天了,咋没有人呢

1、先看仿真有没有问题?

2、如果仿真没问题,看看PCB的仿真,能达到你要求的频率吗?

3、DDR的刷新是官方的IP吗?

4、是不是对同一地址又执行了写操作?

检查下refresh次数丢了没?

谢谢!

1、没有仿真,因为一开始就在板子上调通了,数据写入DDR后没存储多长时间就把数据读出来了,没有什么错误。所以就跳过仿真了。

2、据PCB设计的同事说,PCB仿真也符合要求

3、刷新是官方的IP吗?这个不太懂唉,刷新的控制不是DDR自动进行的吗?

4、没有对同一个地址执行多次写操作,从数据可以看出,错的是其中的某一两个bit

不会检查,待我学了看看。那么刷新次数不对是什么原因影响的呢?DDR手册中的刷新参数是正常温度下7.8us,85摄氏度以上是3.9us,参数是根据手册填的。

是板子设计问题,现在跑很低的频率没问题

refresh逻辑有问题吧,存数据的电跑了?