新手刚学习Modelsim,出现无法仿真,求大神告知如何解决 谢谢。

时间:10-02

整理:3721RD

点击:

二分频器的源程序

二分频器的源程序module divider_frequency(clk_in,rst,clk_out);

input clk_in,rst;

output clk_out;

wire clk_out;

reg clk_temp;

always@(posedge clk_in or negedge rst)

begin

if(!rst)clk_temp=0;

else

clk_temp=~clk_temp;

end

assign clk_out=clk_temp;

endmodule

二分频器的测试程序

`timescale 1ns/1ns

module divider_frequency_tb();

reg clk_in;

reg rst;

wire clk_out;

divider_frequency u0(

.clk_in(clk_in),

.rst(rst),

.clk_out(clk_out)

);

initial

begin

clk_in=0;

rst=0;

#100 rst=1;

end

always#1000 clk_in=~clk_in;

endmodule

求大神。谢谢了

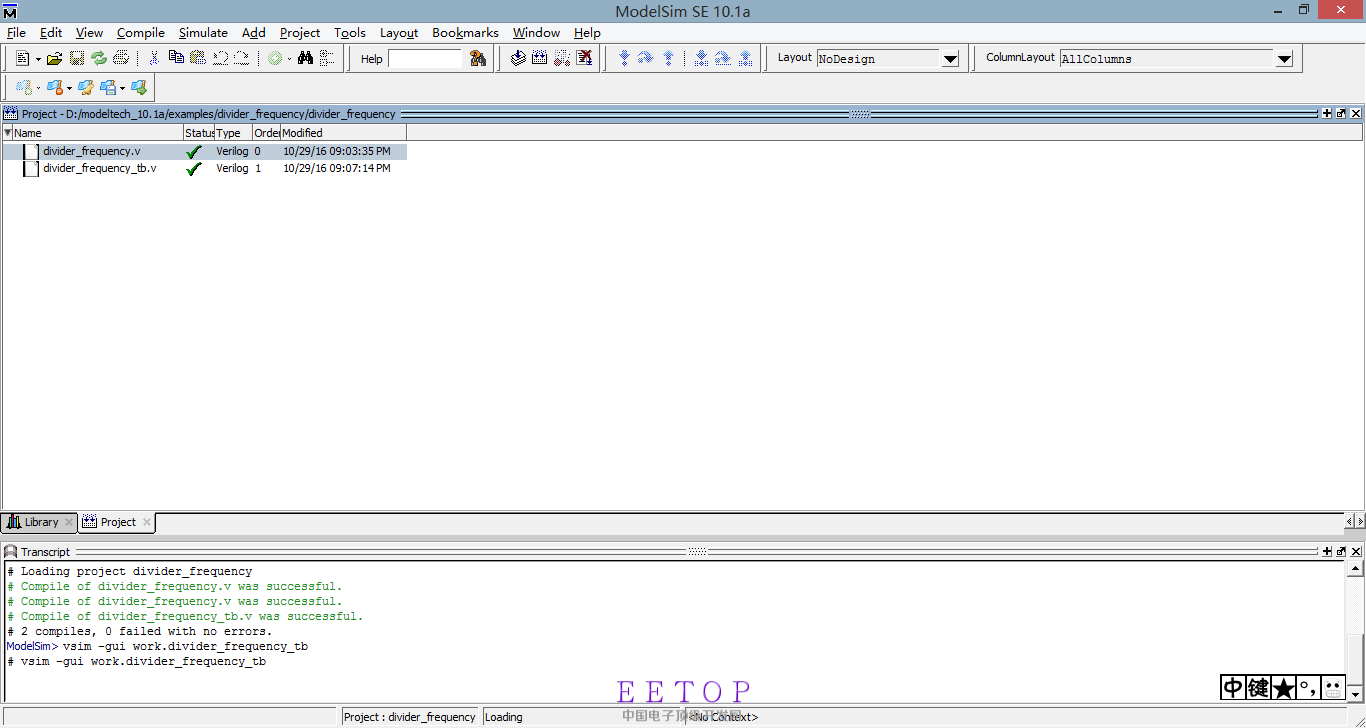

不知道指令,你直接右键需要运行的模块,选运行仿真。下面同样会有命令Log,再对比看看!

还是不行的。在work下对tb文件进行simulate,还是一直在原来的界面不跳转。不会出现添加信号的sim界面