建立时间 保持时间计算

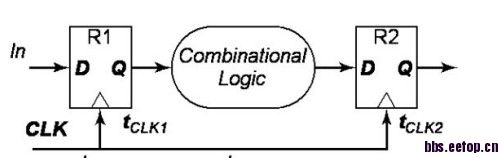

比如说是两个触发器的情况

总的来说,一个数据要想从D端写入Q端,必须有一个延时,这个延时就是建立时间和保持时间相加。

如图,正常来讲当时钟沿到来时R1的D信号要传递到Q端。但是实际电路上需要有两个条件:

1.在clk时钟沿到来之前T1时间里D端应该保持不变。

2.在clk时钟沿到来之后T2时间里D端也因该保持不变。

这里T1,T2就是建立时间和保持时间。

如果没有满足T1,T2,就会有亚稳态出现。

太简单了 谁能讲的详细点,比如建立时间和保持时间怎么计算的?

Tco表示dff从输入到输出延时;Tlogic表示组合逻辑延时;Tsu表示dff的建立时间;Thold表示dff的保持时间。

无skew:

T>Tco+Tlogic+Tsu

Thold<Tco+Tlogic

有skew:

T>Tco+Tlogic+Tsu-Tskew

Thold<Tco+Tlogic-Tskew

同意!

正在学习时序约束,看大了头啊。

5楼,牛

有skew的情况,是不是不能一概而论,也有可能是加上skew?

Tco表示dff从输入到输出延时;Tlogic表示组合逻辑延时;Tsu表示dff的建立时间;Thold表示dff的保持时间。

无skew:

T>Tco+Tlogic+Tsu

Thold<Tco+Tlogic

有skew:

T>Tco+Tlogic+Tsu-Tskew

Thold<Tco+Tlogic-Tskew

这是时序分析的基础,一定要理解

~临时分析就可以了,不用写这么多公式吧。

最近正头大呢

第二个式子不太懂,请问为什么Thold<Tco+Tlogic 呢?

第二个式子不太懂,请问为什么 Thold<Tco+Tlogic 呢?

Tco表示从clk到output Q的延时吧

Tco表示从clk到output Q的延时

个人认为,

在算SETUP时,应该+skew

在算HOLD时,应该-skew

信号既不能传播的太慢,又不能传播的太快。

1. 在两个相邻的clock cycle 中, 如果信号传播的太慢,第二个时钟到来时,信号还没有到达下级的register, 就会导致这一级的register输出不变,出现错误。因此应该有:

Tpcq + TpAB + Tsetup > Tclock_cycle.

2. 在同一个clock cycle 中, 如果信号传播的太快,下一级的register的输出还没有稳定,甚至还没有开始输出(clock skew), 前一级的输出信号就到达了, 正确的信号被覆盖,导致输出错误。 因此有:

Tccq + TcAB < Thold;

Tccq + TcAB < Thold + Tskew.

Tpcq : register的最大输出延时(从 D 到 Q)。

Tccq: register的最小输出延时 (从 D 到 Q)。

TpAB: 两极register之间组合逻辑的最长输出延时。

TcAB: 两极register之间组合逻辑的最小输出延时。

google一下啊

楼上误导,那些公式是通过已知setup-time和hold-time来计算最小时钟周期和污染延迟的,skew偏后对setup-time约束会松点,对hold-time会紧,skew偏前相反。

setup-time和hold-time是由触发器内部结构决定的,主要取决于内部门级延迟包括钟控门延迟,双稳态反馈环建立延迟(双稳态触发器为例),当然还有布线延迟那就不谈了。

setup-time,时钟跳变,主锁存器锁住,从锁存器开启,那么在主锁存器锁住之前,数据应当已经通过主锁存器的双稳反馈建立完全传输到从锁存器,这需要经过门级的延迟,就是setup-time。

hold-time,时钟跳变,隔断主锁存器,这是由于延迟需要一个隔断时间,在此时间内输入应当保持不变防止改变后的数据通过误传入从锁存器。

这些需要都是需要了解内部门级关系计算的,建库会需要,而拿到库文件一般都会给出来的。

个人觉得,skew应该都是往偏紧的约束……

第二个式子不太懂,请问为什么Thold<Tco+Tlogic 呢?

好难