我无语了,求高手

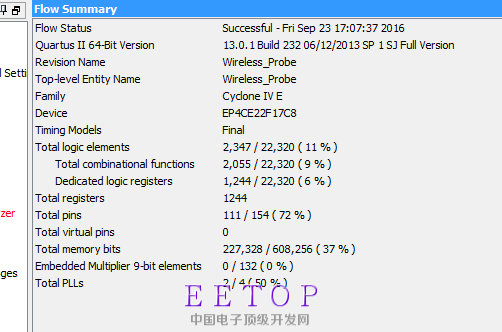

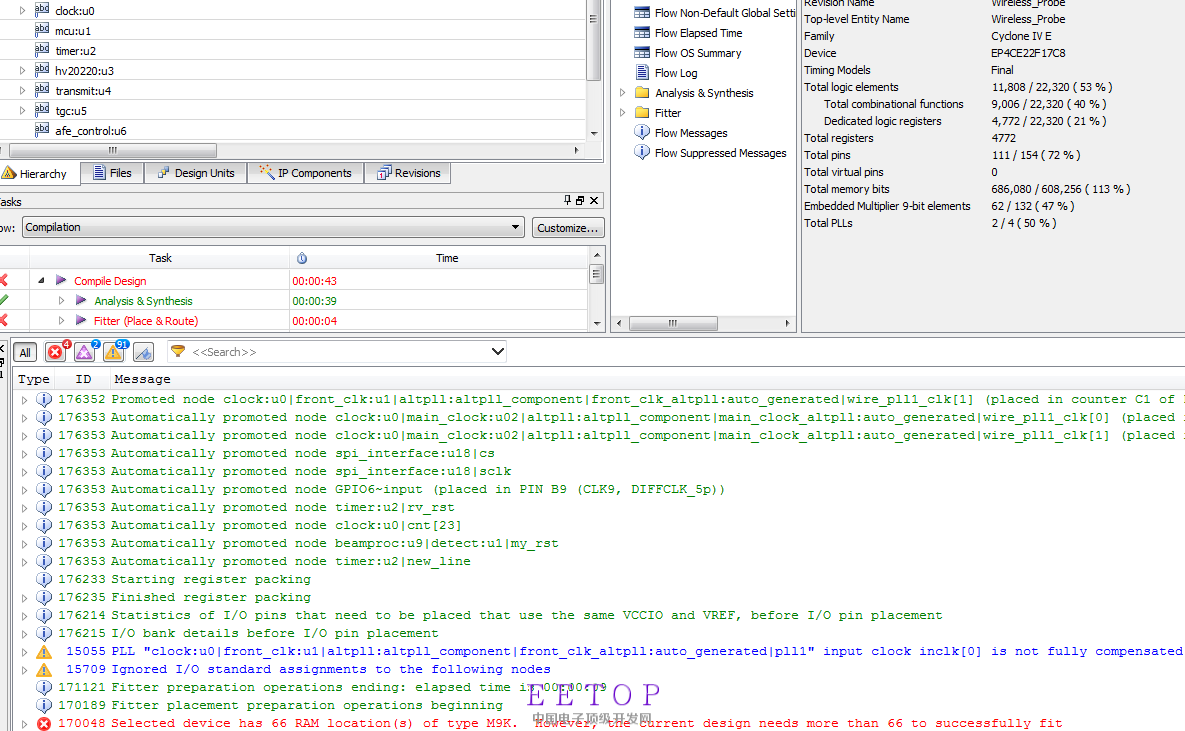

加上ALTSQRT核后,资源立马不够用,如下:

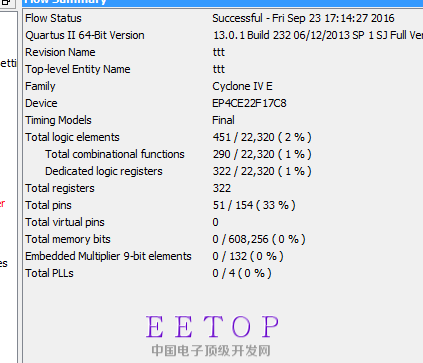

可以问题好像不是资源的问题,我建一个工程单独测试ALTSQRT,所占资源非常少,如下:

这是为什么啊,单独测的时候资源占用这么少,加到工程里面占用为什么这么大呢?选择的参数是一样的!

看起来是您的IO PIN 太多了,IP CORE 和

IP CORE之间的连接也会占用LAB资源,您需要考虑改变IO 接口彼此连接的方式,例如采用IN OUT 分离,不要有Z TYPE 出现,因为Z TYPE 要增加

BUS HOLDER的空间跟CELL。

我的IP PIN硬件电路决定了这部分改不了,

至于IO类型你说的Z TYPE是指INOUT 类型吗? 我只定义了INPUT OUTPUT 两种IO类型

并没有定义INOUT的IO类型啊

您的资源增加主要有两项

一个是IO ,另一个是register

假设IO 是IP CORE 定死了那就不好解题了。所以只能注意另一个register的问题。

请注意您的code 中是否有使用

if then else

如果有,它是否是刻意要形成register 的语法如果是,那它应该搭配

CLK 来形成,如果不是,则应该

使用

if then else 完全语句描述它,不能把else 漏掉,如果没有else ,则then 内的变量全部会形成latch type 电路,而占用regitser 资源消耗,when ,或是其它条件式语法都一样,不想形成latch type 电路,都要用完全列举条件式写,不能漏,列不完可以用

others指令;

如果这两项你都注意到了,那就有其它问题,那就难了。

(VHDL : 语法下

宣告

outname : out std_logic ;

Enpin: in std_logic;

使用

Outname<= register_out when Enpin=’1’else ‘Z’;

这种语法就会形成IO PIN 使用Z-type会额外占据

LAB 资源。只适合用在外部IO PIN,而不适合内部连接。)

首先感谢你的分析,

不过有一点,在没加入SQRT这个核的时候资源占用并不算多,仅仅加了个SQRT核(别的没有任何改动)

,资源一下就没有了,根据报告一个SQRT核所用的资源比之前全部加起来还要多的多,

而单独测SQRT核的时候占用资源并不多!

如果像你说的,在没加SQRT的时候那些问题就已经存在了,没加SQRT的时候占用资源就应该已经很多了才对,加SQRT的时候并没有引用别的语句啊

您的资源不够用是出现在 total memory bits 的问题上

68080/608256 (113%) 100是用满。已经超过了。

请检查这项是哪里使用的。

在加入SQRT之前只用了37% 加入之后就成113%,所以应该是SQRT的加入导致了更多MEM的使用,

我得再好好看看代码!你给了我启示,非常感谢!

好像还不对,我原来以为去掉SQRT后,可能会有一系列RAM因为输出没有被用到,会被优化掉,可我又看看了,虽然前面有很多RAM,不过没有RAM的输出给SQRT,也没有RAM用到SQRT的输出,看来还得仔细查下了!