低频时钟采高频时钟生成的脉冲

时间:10-02

整理:3721RD

点击:

比如150M时钟采5ns的脉冲上升沿,怎么做?

set_false_path -from [get_clocks clock] -to [get_ports Asynch_in]

异步时钟域之间不能进行STA,设置false path就可以了

是单独的一个脉冲还是周期性的脉冲。

5ns对应200MHZ,如果是单独的,应该不能够稳定的采集到。

我也不晓得怎么采,等高手来。

可以把高频脉冲展宽

单脉冲

展宽得在高频时钟域做,现在只有低频域可以处理的话咋办?把信号接到触发器的clk管脚是否合适?可它又不是时钟信号,不知道综合时能不能通过。

不符合采样定理,采不了。

要么展宽,要么用同步时钟采。

做成异步就可以了,直接接时钟端

跟我在5楼说的方法一样?会不会有综合不通过的情况?

set_false_path -from [get_clocks clock] -to [get_ports Asynch_in]

异步时钟域之间不能进行STA,设置false path就可以了

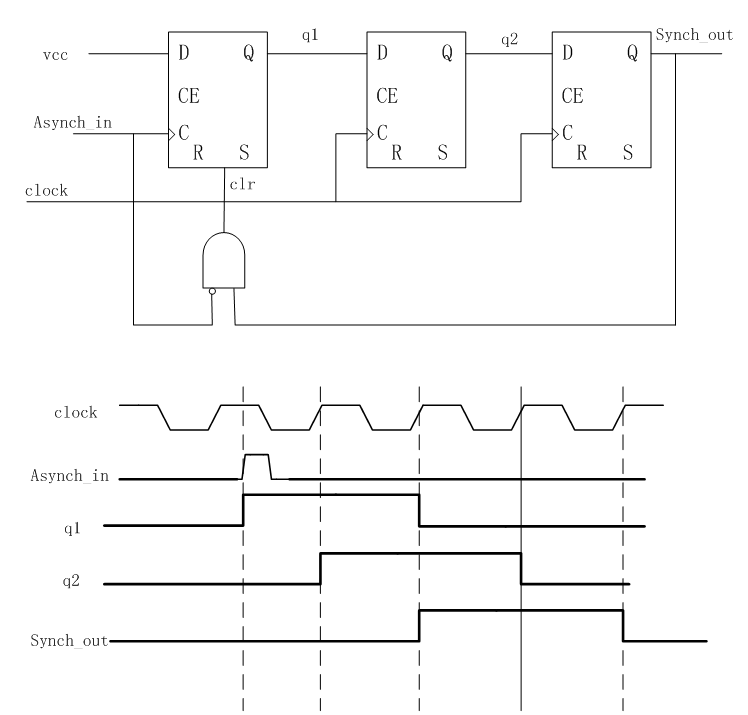

你的意思是异步脉冲接到clk端,然后做同步处理,综合时set false path不做时序分析? RTL编码是不是这样:

always@(posedge asynch_in or posedge clr)

begin

if(clr)

q1<= 0;

else

q1<= 1;

end

always@(posedge clock)

begin

q2<= q1;

synch_out<= q2;

end

assign clr = ~asynch_in & synch_out;

好巧妙。

是的,如果不能在快时钟域处理,这种窄脉冲信号也只能用这种方法采样了,综合的时候异步时钟域需要设置false path,用两级触发器来解决 亚稳态问题,还有你代码中最好再加上本时钟域的复位信号。

synthesis 当然可以过。你create clk/generated clk, then 设置clk group保证特殊clk domain的STA check 即可

thx~

3Q

受教了!