spartant 6 MCB读写DDR3的问题

时间:10-02

整理:3721RD

点击:

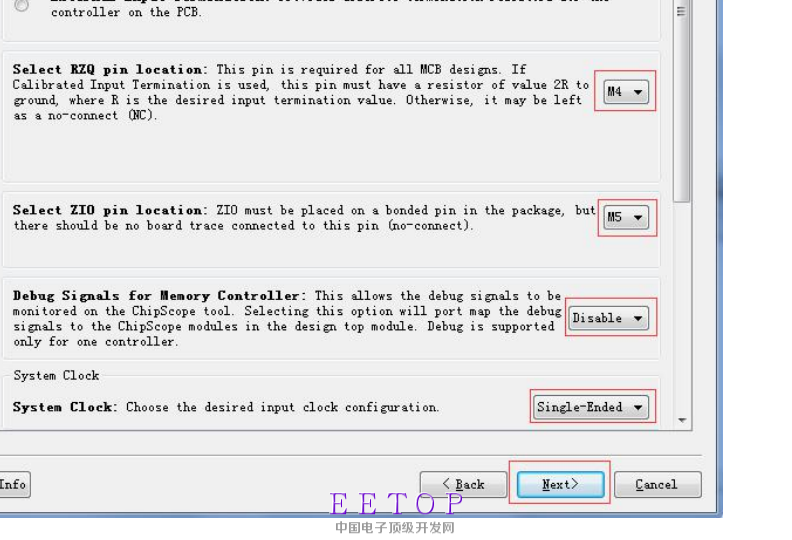

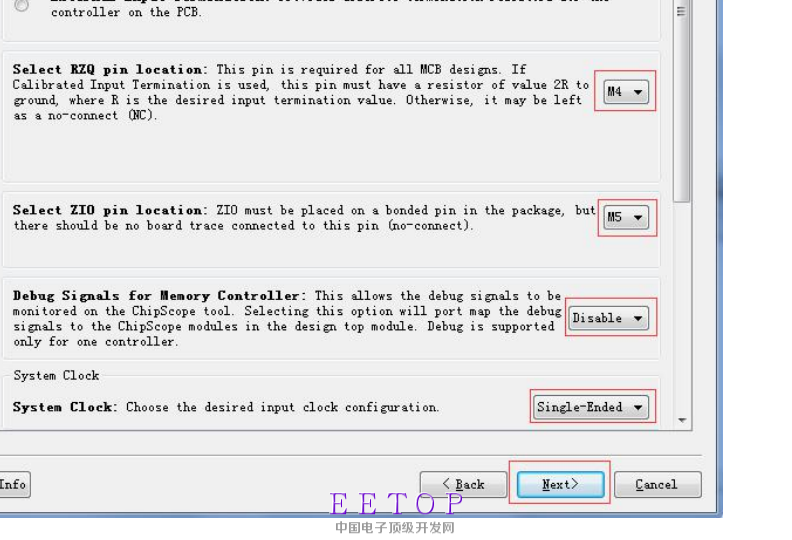

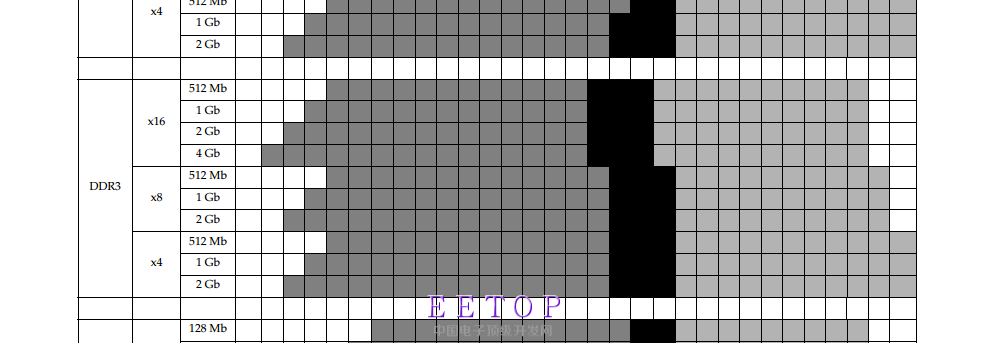

各位GGJJ好,小弟最近调试米联的mis603板子上面挂载两片ddr3,例程里面用的MCB硬核来控制DDR3读写。在配置port的时候才用port0 128 bits 这里需要设置RZQ ZIO(一个是校准信号完整性,一个矫正输出阻抗),我怎么知道这两个信号的位置,还是这两个信号的位置在布局pcb的时候就已经定了?

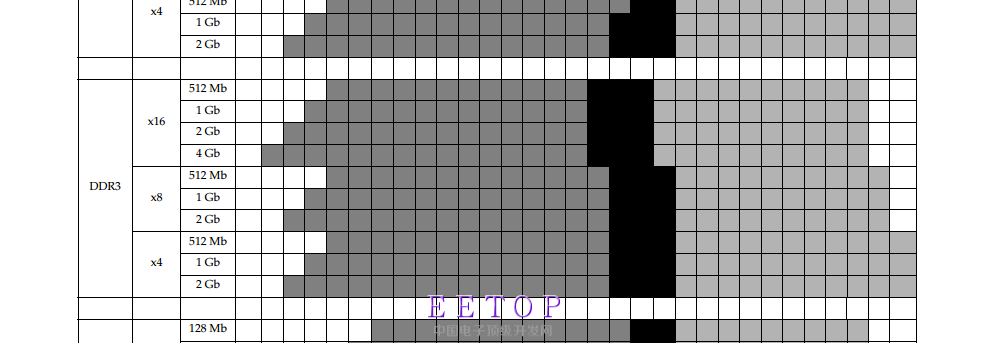

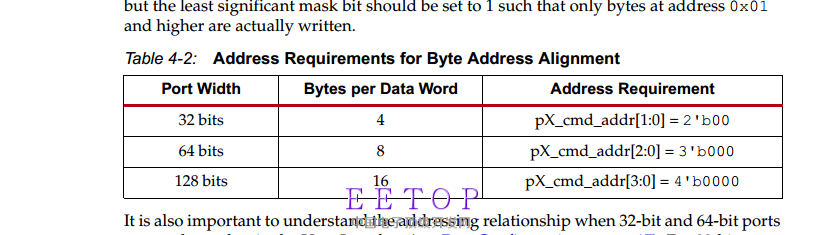

2,我的ddr3容量为128mx16 也就是我的行地址+列地址+bank地址=27,而px_cmd_addr[29:0]此处地址线为30位,但是对于128mx16来说只用了27位 即 px_cmd_addr[27:1]刚好可以映射到我的存储器地址总线 和bank上对么

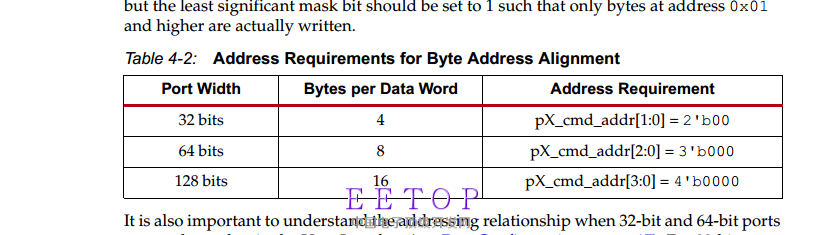

3.我参考UG388 如果我才用128bit的话 以dq=8为例,本地端每次传送128bit也就是16个字节,对应到ddr3上面16个地址空间,但是我只用了px_cmd_addr[27:1] 相当于我一次传输只映射到了ddr3上 8个地址空间 这不想矛盾了么

望GGJJ 不吝赐教 小弟谢过

2,我的ddr3容量为128mx16 也就是我的行地址+列地址+bank地址=27,而px_cmd_addr[29:0]此处地址线为30位,但是对于128mx16来说只用了27位 即 px_cmd_addr[27:1]刚好可以映射到我的存储器地址总线 和bank上对么

3.我参考UG388 如果我才用128bit的话 以dq=8为例,本地端每次传送128bit也就是16个字节,对应到ddr3上面16个地址空间,但是我只用了px_cmd_addr[27:1] 相当于我一次传输只映射到了ddr3上 8个地址空间 这不想矛盾了么

望GGJJ 不吝赐教 小弟谢过

你图上不是写的很清楚了,它们对应的位置就是:M4,M5。 这个在例化MCB时就指定的。

我最近也在搞这个,可以交流一下,79685956