关于虚假路径的问题

(1)约束一条路径为虚假路径,那么这条路径所要达成的功能,是否就无法实现?

(2)约束一条路径为虚假路径,是否只是在时序分析时,不分析这条路径,对最终生成的SOF文件没有影响。

望大神们帮我解答一下,谢谢。

首先,之所以把一条路径设为false path,是因为designer确认虽然这条path是物理存在的,但是逻辑上没有信号会穿过这条path。

比如下面这条path:

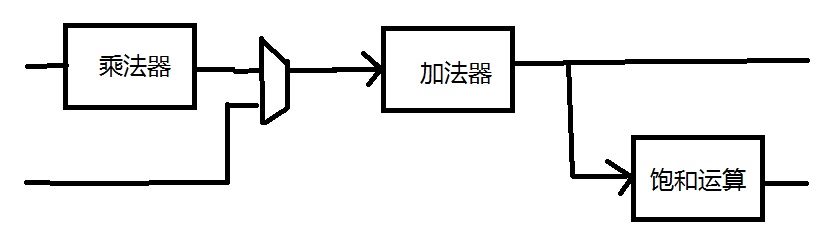

有一条指令是做乘累加运算:a*b+c

另一条指令是做加法和饱和运算:a+b -> saturation

但是没有一条指令会做:a*b+c -> saturation 运算

逻辑上肯定没有信号会流过这样一条false path(物理上有,但是不会影响DC的timing check),所以designer就将这条path设为false path来告诉DC不用检查这条path的setup time和hold time。因为不会有任何运算需要依次经过乘法,加法,饱和三个操作然后检查setup time

请问如果在时序逻辑中,跨时钟域,两个异步时钟设置为false path,工具也就不分析他们之间的路径了吧,这样用可以吗

没做过跨时钟域的,但是理论上是可以这么做的。关键是你作为设计者必须明白自己的设计,如果实际上这条path是存在的,你把它设为false path,只是告诉DC不要分析这条路径,虽然DC能够通过,但是最终的芯片里如果这条path不满足时序要求还是不能工作。

你的意思也就是说约束为虚假路径对最终生成的电路没有什么影响,只是在时序分析的时候告诉软件,你不用检查了,是这个意思吧!谢谢大神

如果你很了解自己的设计,设置的false路径也对,应该没有问题

如果设置false路径出现错误呢:

比如不应该约束为false的你约束了,那么实际流片后芯片可能不能正常工作;

应该设置为false的你没有设置,工具会费很大的气力去约束,带来的的是面积代价的工作速度的代价;当然也有可能工具会报出error,那样你就会重新审视这条路径,如果你还没发现它是个false路径,你可能会修改代码。

我也不是做后端的,想到哪就说了,抛砖引玉吧

不懂,太深奥,我记得ISE约束中跨时钟域只需要约束时钟之间的频率和相位关系就可以了

3楼正解,将物理上存在、逻辑上不存在的路径设为 false path,就是告诉DC不需要对这条路径进行时序优化。(这样就可以使用面积更小的cell,对SDF文件肯定是有影响的,小编说的SOF应该是SDF吧?)

false path 的设定更多的是用在跨时钟域情况下,对异步信号进行时序分析的是没有任何意义的,因为它们本来就没有任何的相位关系。

我说的sof是下载文件,不是sdf,那室延时文件把!